## Practical Erase Suspension for Modern Low-latency SSDs

**Shine Kim<sup>†§</sup>** Jonghyun Bae<sup>†</sup> Hakbeom Jang<sup>\*</sup> Wenjing Jin<sup>†</sup> Jeonghun Gong<sup>†</sup> Seoungyeon Lee<sup>§</sup> Tae Jun Ham<sup>†</sup> Jae W. Lee<sup>†</sup>

July 12<sup>th</sup>, 2019

§SAMSUNG Electronics

\*Sungkyunkwan University

**USENIX ATC 2019, RENTON, WA, USA**

### **NAND Flash-based SSD**

## **1) Superior Throughput** (e.g., Sequential Read $\rightarrow$ 6.4GB/s)

## 2) Low average Latency (e.g., 4KB Random Read QD1 → 15us)

3) Relatively Low Price (e.g., QLC SSD  $\rightarrow$  0.1\$/GB)

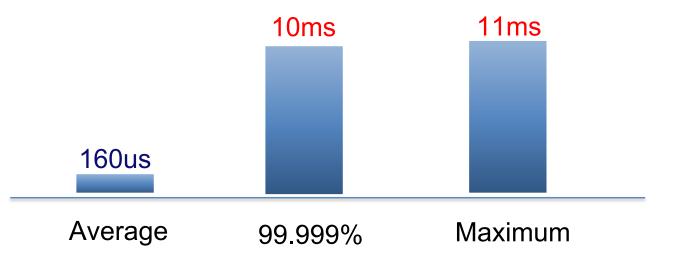

## **Read Latency**

(4KB Random, Read 70%, Write 30%, QD 16)

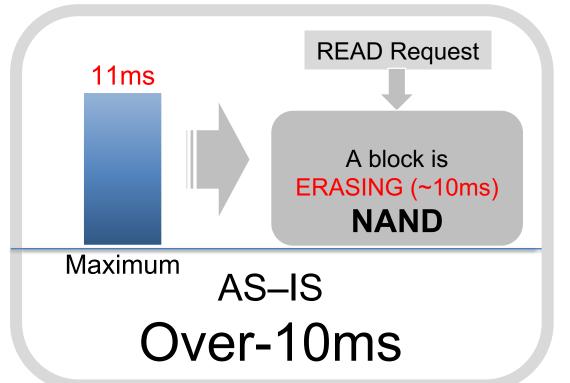

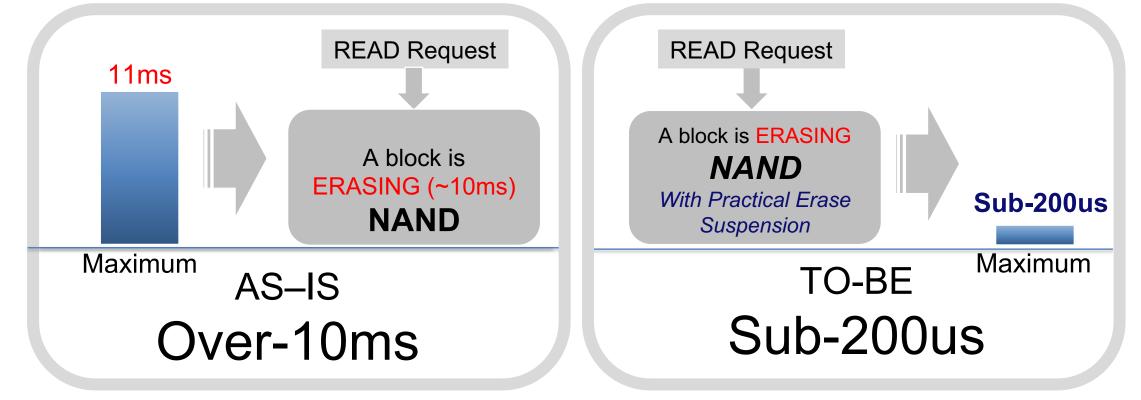

## The source of long read tail latency

## **Read Tail Latency**

(4KB Random, Read 70%, Write 30%, QD 16)

## The source of long read tail latency

## **Read Tail Latency**

(4KB Random, Read 70%, Write 30%, QD 16)

## The source of long read tail latency

## **Read Tail Latency**

(4KB Random, Read 70%, Write 30%, QD 16)

Architecture and Code Optimization (ARC) Laboratory @ SNU

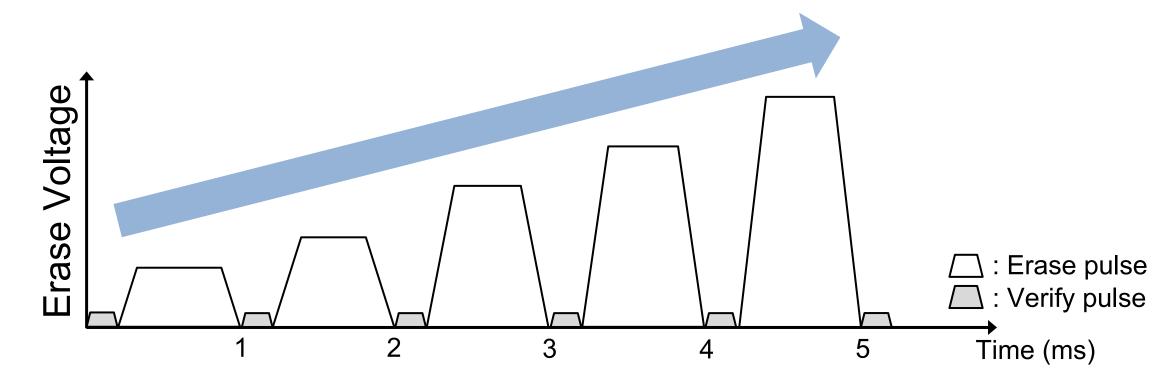

## Incremental Step Pulse Erasing (ISPE) scheme

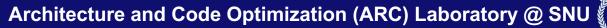

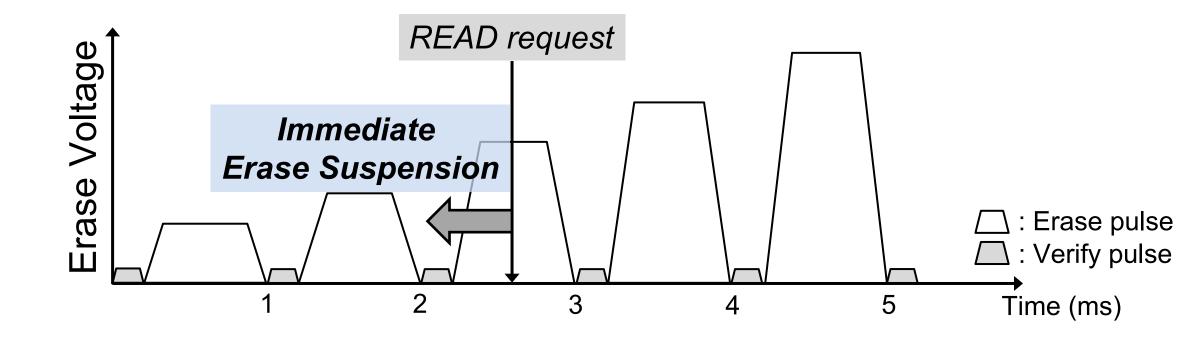

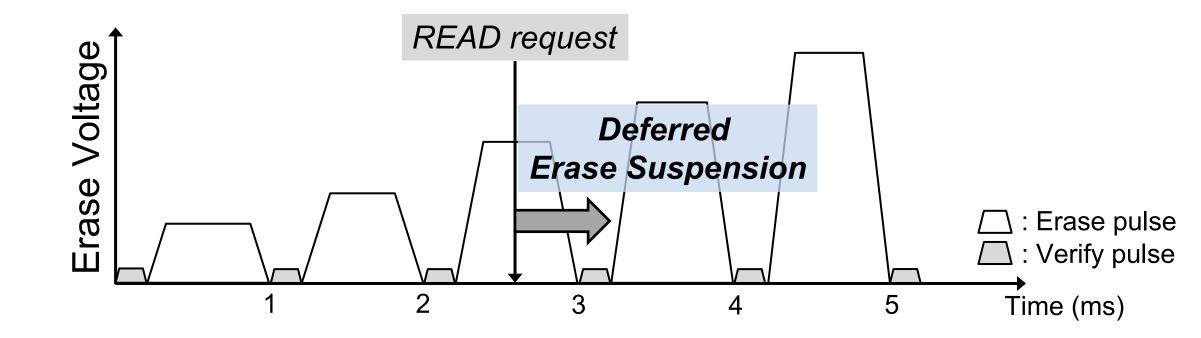

## Suspending/Resuming at well-aligned safe points

## Suspending/Resuming at well-aligned safe points

## Suspending/Resuming at well-aligned safe points

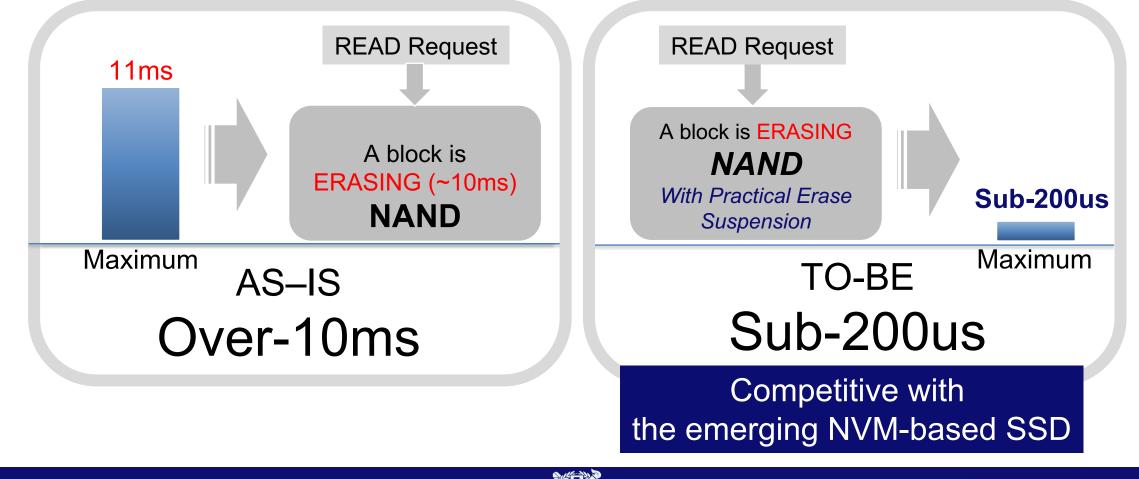

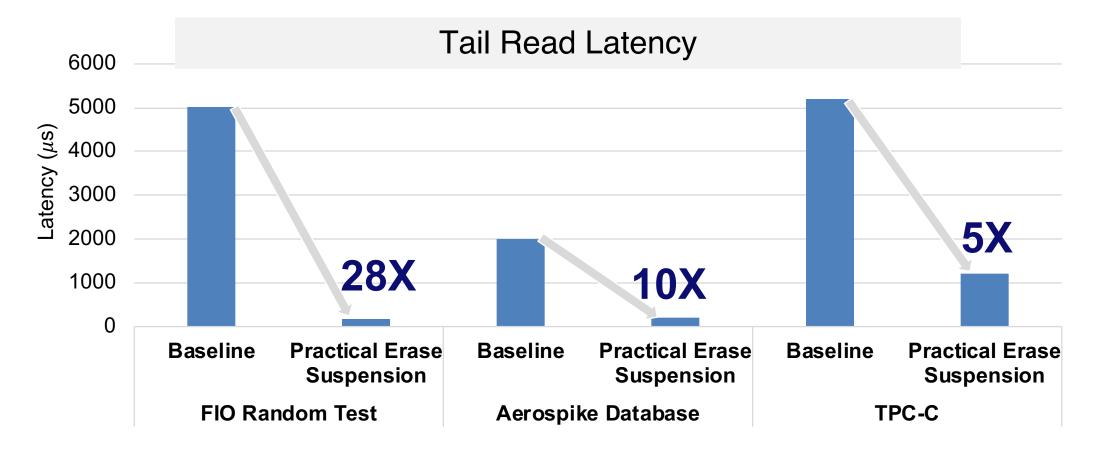

#### **Summary**

Practical erase suspension harnesses the full potential of NAND flashbased SSDs

#### Summary

Practical erase suspension harnesses the full potential of NAND flashbased SSDs

Architecture and Code Optimization (ARC) Laboratory @ SNU

# Thank You ③

## USENIX ATC'19 Track I Solid-State & Hard Disk Drives Session July 12<sup>th</sup> 09:55am

Architecture and Code Optimization (ARC) Laboratory @ SNU