# Unioning of the Buffer Cache and Journaling Layers with Non-volatile Memory

**USENIX FAST '13**

Eunji Lee (Ewha University, Seoul, Korea)

Hyokyung Bahn (Ewha University)

Sam H. Noh (Hongik University)

#### **Outline**

- Reliability issues in storage systems

- Non-volatile memory as a solution

- UBJ: Unioning of Buffer cache and Journaling

- Performance evaluation

# A man working hard ...

### A man working hard ...

A problem has been detected and windows has been shut down to prevent damage to your computer. SYSTEM PAGE\_FAULT\_IN\_NONPAGED\_AREA If this is the first time y CRASH or screen, restart your computer. If t n. follow these steps: Check to make sure any new properly installed. software manufacturer PLEASE WAIT... If this is a new installati for any Windows updates you If problems continue, disab nstalled hardware or software. Disable BIOS m ching or shadowing. If you need to use Safe Mod components, restart your computer, press F8 to Options, and then select Safe Mode. Technical information: \*\*\* STOP: 0x00000050 (0x80010205,0x00000001,0x8B5982A5,0x00000000)

### So what happened?

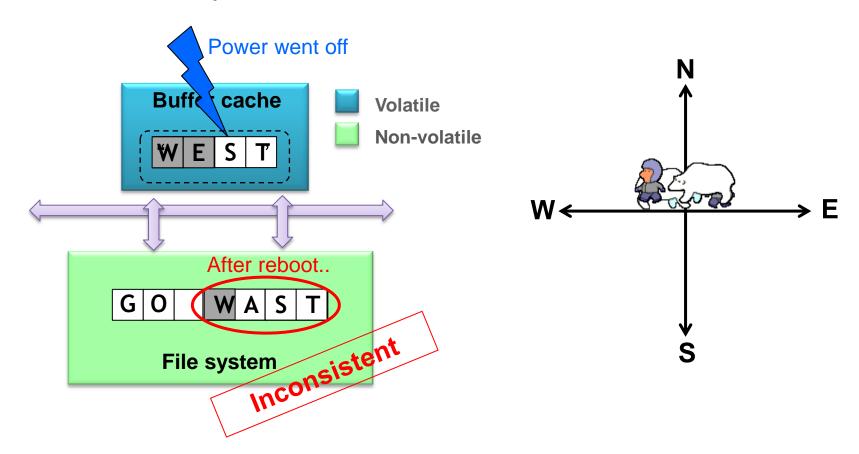

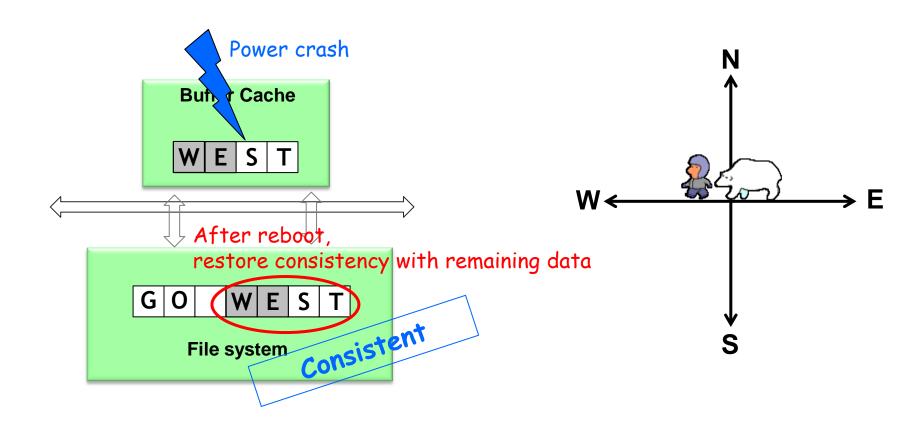

Sudden power failure incurs file system inconsistency

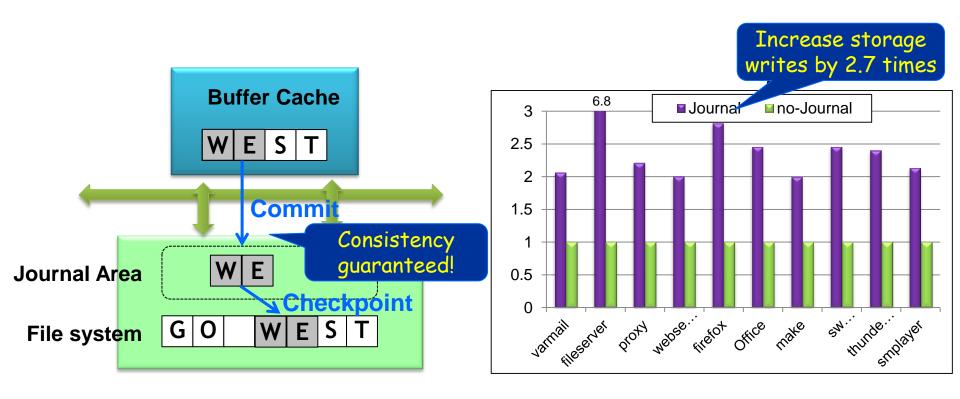

### Journaling as a solution

- Prevent data inconsistency through write-twice

- ext4, ReiserFS, XFS, btrFS ...

# Non-volatile memory as a solution

#### Non-volatile memory as main memory

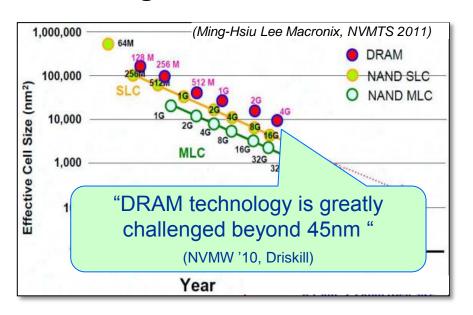

#### 1. Scaling Limit of DRAM

#### 2. Power consumption

As much as 40% of the total system energy is consumed by the main memory subsystem in a mid-range IBM eServer machine. (Querish, ISCA 2009)

Replacing DRAM with STT-RAM in data centers can reduce power by up to 75% (NVMW '10, Driskill)

#### 3. Demand for fast memory access

As critical applications are becoming more data-centric, memory performance is fast becoming the key bottleneck

# **Non-volatile Memory Technology**

Source: T. Perez, C. A. F. D Rose, Technical Report, PUCRS, 2010

|               | SRAM                        | DRAM               | Disk                 | NAND<br>Flash      | PCRAM                     | RRAM<br>(Memristor)  | MRAM<br>(STT-RAM)    |  |  |

|---------------|-----------------------------|--------------------|----------------------|--------------------|---------------------------|----------------------|----------------------|--|--|

| Maturity      | Product                     | Product            | Product              | Product            | Advanced development      | Early<br>development | Advanced development |  |  |

| Cell Size     | >100 F <sup>2</sup>         | 6-8 F <sup>2</sup> | (2/3) F <sup>2</sup> | 4-5 F <sup>2</sup> | 8-16 F <sup>2</sup>       | >5 F <sup>2</sup>    | 37 F <sup>2</sup>    |  |  |

| Read          | <10 ns                      | 10-60 ns           | 8.5 ms               | 25 μs              | 48 ns                     | <10 ns               | <10 ns               |  |  |

| Latency       |                             |                    |                      |                    |                           |                      |                      |  |  |

| Write         | <10 ns                      | 10-60 ns           | 9.5 ms               | 200 μs             | 40-150 ns                 | ~10 ns 12.5 ns       |                      |  |  |

| Latency       |                             |                    |                      |                    |                           |                      |                      |  |  |

| Energy per    | >1 pJ                       | 2 pJ               | 100-                 | 10 nJ              | 100 pJ                    | 2 pJ                 | 0.02 pJ              |  |  |

| bit access    |                             |                    | 1000 mJ              |                    |                           |                      |                      |  |  |

| Static Power  | Yes                         | Yes                | Yes                  | No                 | No                        | No                   | No                   |  |  |

| Endurance     | >1015                       | >1015              | >1015                | 10 <sup>4</sup>    | 10 <sup>8</sup>           | 10 <sup>5</sup>      | >1015                |  |  |

| Nonvolatility | No                          | No                 | Yes                  | Yes                | Yes                       | Yes                  | Yes                  |  |  |

|               | Current Memory Technologies |                    |                      |                    | Emerging NVM Technologies |                      |                      |  |  |

| Scalability | Low-power | High-performance |  |

|-------------|-----------|------------------|--|

|             | • —       |                  |  |

# Non-volatile Memory Technology

Source: T. Perez, C. A. F. D Rose, Technical Report, PUCRS, 2019

|               | , , , , , , , , , , , , , , , , , , , |                    |                      |                    |   | 7                   |    | _                 |   |                   |

|---------------|---------------------------------------|--------------------|----------------------|--------------------|---|---------------------|----|-------------------|---|-------------------|

|               | SRAM                                  | DRAM               | Disk                 | NAND               | Ī | PCRAM               |    | RRAM              |   | MRAM              |

|               |                                       |                    |                      | Flash              |   |                     |    | (Memristor)       | Ц | (STT-RAM)         |

| Maturity      | Product                               | Product            | Product              | Product            | ı | Advanced            |    | Early             |   | Advanced          |

| •             |                                       |                    |                      |                    |   | development         |    | development       | П | development       |

| Cell Size     | >100 F <sup>2</sup>                   | 6-8 F <sup>2</sup> | (2/3) F <sup>2</sup> | 4-5 F <sup>2</sup> | I | 8-16 F <sup>2</sup> |    | >5 F <sup>2</sup> |   | 37 F <sup>2</sup> |

| Read          | <10 ns                                | 10-60 ns           | 8.5 ms               | 25 μs              | Τ | 48 ns               |    | <10 ns            | П | <10 ns            |

| Latency       |                                       |                    |                      |                    |   |                     |    |                   |   |                   |

| Write         | <10 ns                                | 10-60 ns           | 9.5 ms               | 200 μs             |   | 40-150 ns           |    | ~10 ns            | П | 12.5 ns           |

| Latency       |                                       |                    |                      |                    |   |                     |    |                   |   |                   |

| Energy per    | >1 pJ                                 | 2 pJ               | 100-                 | 10 nJ              |   | 100 pJ              |    | 2 pJ              |   | 0.02 pJ           |

| bit access    |                                       |                    | 1000 mJ              |                    |   |                     |    |                   | П |                   |

| Static Power  | Yes                                   | Yes                | Yes                  | No                 |   | No                  |    | No                |   | No                |

| Endurance     | >1015                                 | >1015              | >1015                | 104                |   | 10 <sup>8</sup>     |    | 105               |   | >1015             |

| Nonvolatility | No                                    | No                 | Yes                  | Yes                | I | Yes                 |    | ⁄es               |   | Yes               |

|               | Current Memory Technologies           |                    |                      |                    |   | Emerg               | ir | g NVM Techr       | o | logies            |

|               |                                       |                    |                      | 1                  |   | 7                   |    | C                 |   |                   |

High-performance V

(Optimistic expectations)

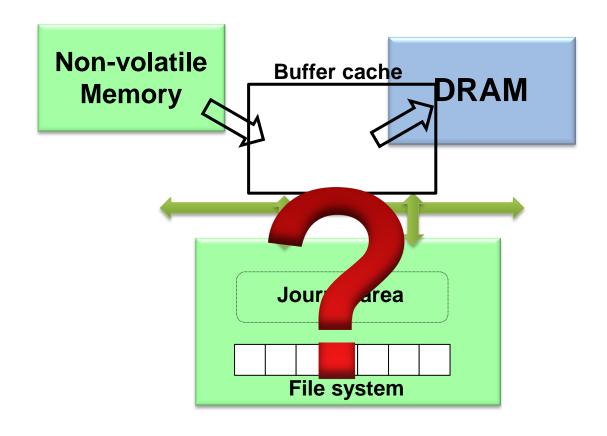

### Non-volatile memory as a solution

Seems to provide data consistency

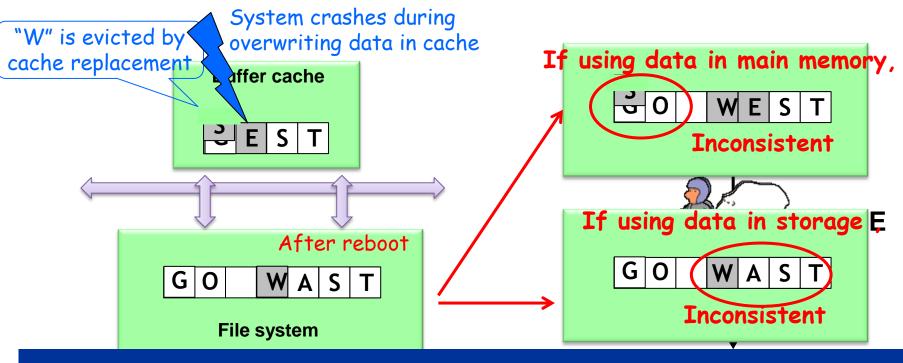

#### Non-volatile memory as a solution?

✓ Inconsistency problem still exists with NVM

Drop-in replacement of non-volatile memory does not suffice

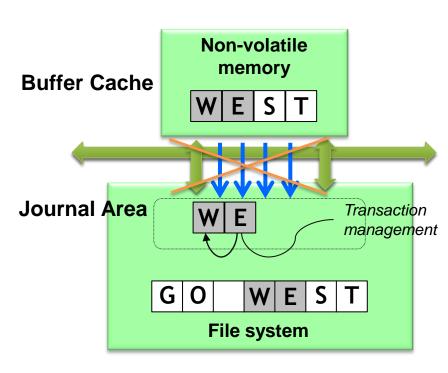

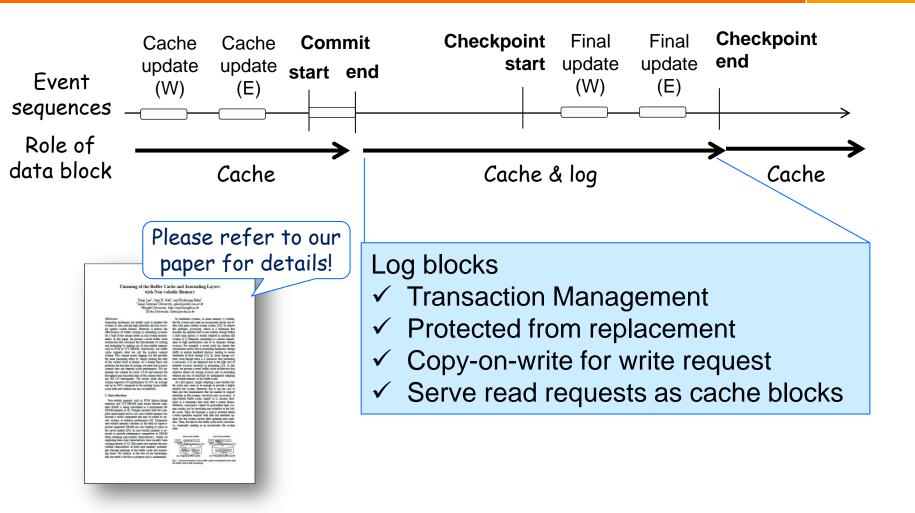

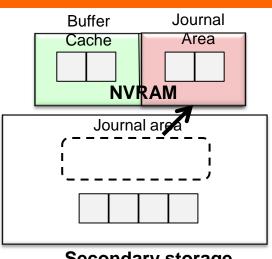

# Unioning of Buffer cache and Journaling Layers (UBJ)

- Provide data consistency without sacrificing performance

- Design a novel buffer cache architecture "UBJ"

- Subsume functions of caching and journaling

- Use data block for dual purposes

- Provide journaling effect through transition of cache block state

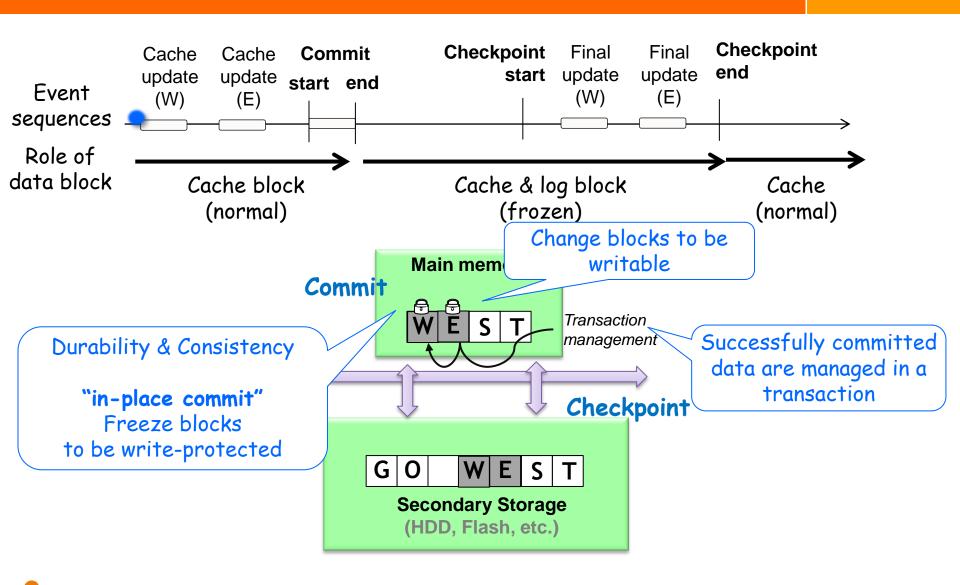

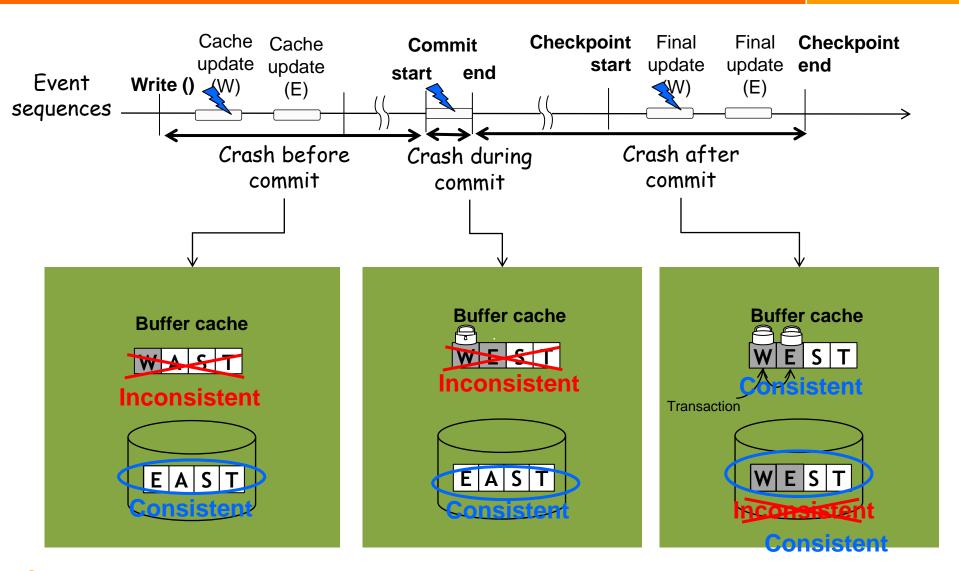

# **Workings of UBJ**

# Workings of UBJ

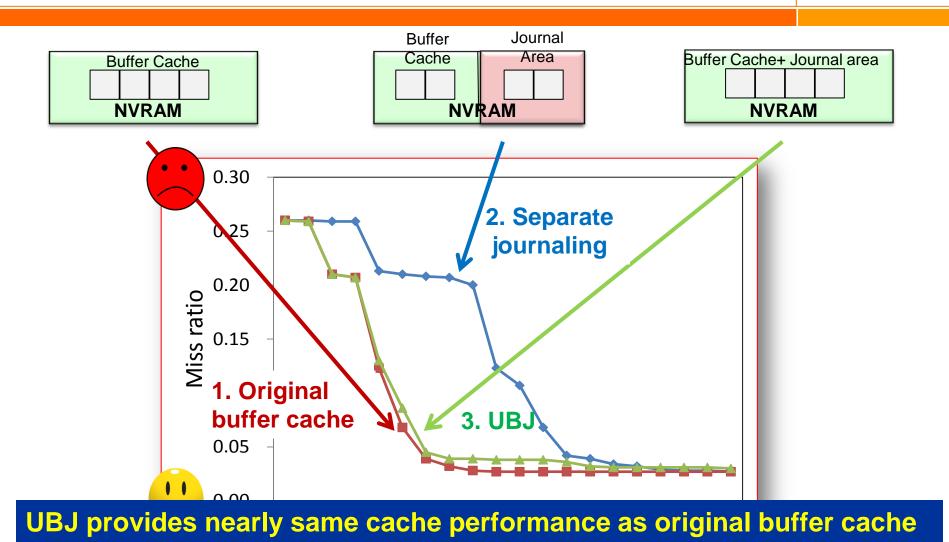

# Cache performance of UBJ

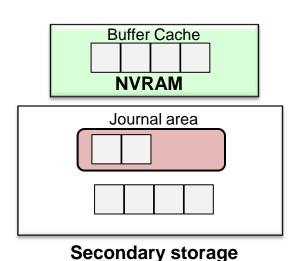

1. Original buffer cache

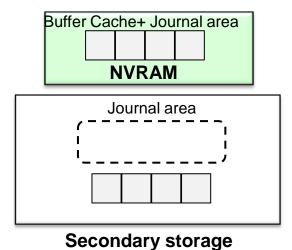

Secondary storage

2. Separate journaling

3. UBJ

### Cache performance of UBJ

cache ratio

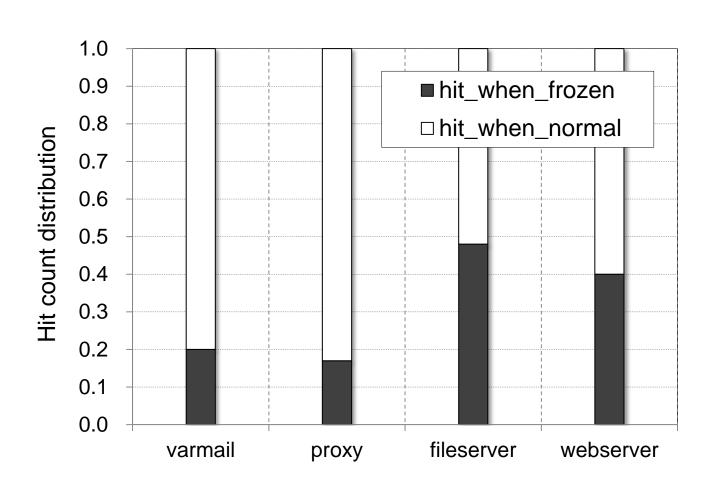

#### Cache hits on frozen data blocks

# System recovery

- Prototype of UBJ on Linux 2.6.38

- Intel Core i3-2100 CPU

- 3.1GHz and 4GB of DDR2-800 memory

- Emulate non-volatile memory with DRAM

- Compare with ext4 in journal-mode

- logs both data and metadata

- Three benchmarks

- Filebench, IOzone, Postmark

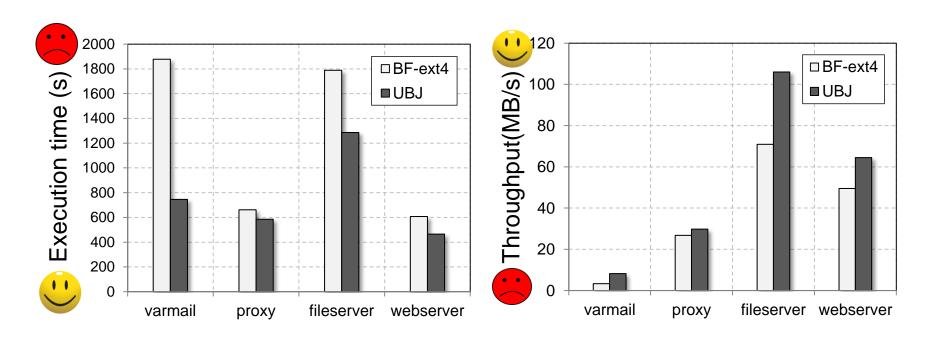

#### Filebench

Improve execution time and throughput by 30.7% and 59.8% on average

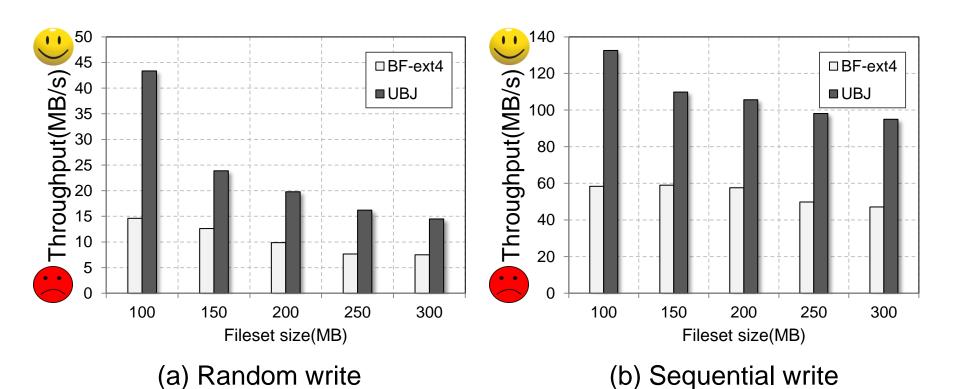

#### IOzone

Improve performance by 110% on average, up to by 240%

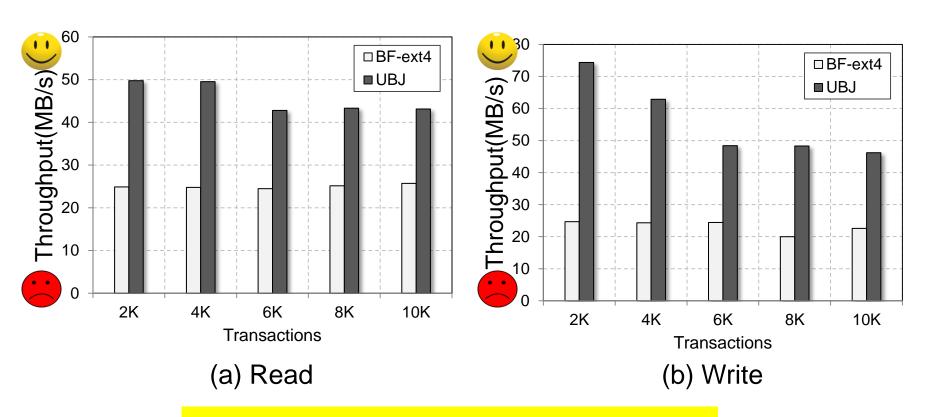

#### Postmark

Improve performance by 109% on average

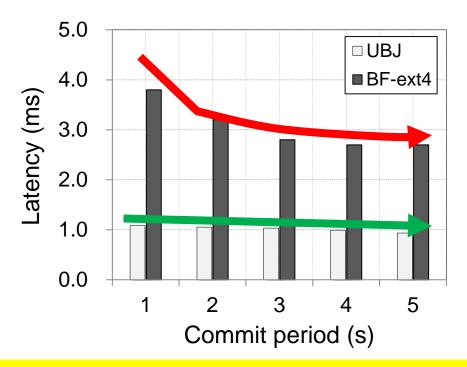

Effectiveness of UBJ on performance as the commit period changes

Latency of ext4 becomes smaller as the commit period is longer Latency of UBJ is not sensitive to the commit period changes

#### **Conclusion**

- Novel non-volatile memory buffer cache architecture

- Subsumes the functions of caching and journaling

- Buffer cache blocks ← → Journal logs

- In-place Commit

- Notion of a frozen state

- Performance results

- Implemented on Linux 2.6.38

- Compared to ext4 in journal mode

- Improve I/O performance by 76% and up to 240%

# Thank you

Eunji Lee <a href="https://sites.google.com/site/alicia0729">https://sites.google.com/site/alicia0729</a>

Hyokyung Bahn <a href="https://home.ewha.ac.kr/~bahn">https://home.ewha.ac.kr/~bahn</a>

Sam H. Noh <a href="https://next.hongik.ac.kr">https://next.hongik.ac.kr</a>