# 2023 USENIX Annual Technical Conference

Boston, MA, USA July 10–12, 2023

oston, MA, USA July 10–12, 2023

# **USENIX ATC '23 Sponsors**

# **Gold Sponsors**

# **Silver Sponsor**

# **Bronze Sponsors**

**General Sponsor**

**Open Access Sponsor**

# **USENIX Supporters**

## **USENIX Patrons**

Amazon • Futurewei • Google • Meta

## **USENIX Benefactors**

Bloomberg • NetApp

## **USENIX Partners**

Thinkst Canary • Two Sigma

# **Open Access Supporter**

Google

# **Open Access Publishing Partner**

PeerJ

## **USENIX** Association

# Proceedings of the 2023 USENIX Annual Technical Conference

#### © 2023 by The USENIX Association

#### All Rights Reserved

This volume is published as a collective work. Rights to individual papers remain with the author or the author's employer. Permission is granted for the noncommercial reproduction of the complete work for educational or research purposes. Permission is granted to print, primarily for one person's exclusive use, a single copy of these Proceedings. USENIX acknowledges all trademarks herein.

ISBN 978-1-939133-35-9

## **Conference Organizers**

**Program Co-Chairs**

Julia Lawall, Inria

Dan Williams, Virginia Tech

**Program Committee**

Reto Achermann, University of British Columbia

Godmar Back, Virginia Tech Saurabh Bagchi, Purdue University Jia-Ju Bai, Tsinghua University

Yungang Bao, Institute of Computing Technology, Chinese Academy of Sciences

Yaniv Ben-Itzhak, VMware Research

Annette Bieniusa, Technische Universität Kaiserslautern

Roberto Bifulco, NEC Laboratories Europe

Laurent Bindschaedler, Max Planck Institute for Software

Systems (MPI-SWS)

Eleanor Birrell, *Pomona College* William Bolosky, *Microsoft*

Philippe Bonnet, IT University of Copenhagen

Sara Bouchenak, *INSA Lyon* Nathan Bronson, *Rockset*

Maria Carpen-Amarie, Huawei Zurich Research Center

Somali Chaterji, *Purdue University* Lydia Chen, *Delft University of Technology*

Yu Chen, Tsinghua University

Young-ri Choi, UNIST (Ulsan National Institute of Science and Technology)

David Cock, ETH Zurich Dave Dice, Oracle

Thaleia Dimitra Doudali, IMDEA Software Institute

Abhinav Duggal, *Dell EMC* Eric Eide, *University of Utah*

Dan Feng, Huazhong University of Science and Technology

Xinwei (Mason) Fu, Amazon Web Services

Wei Gao, University of Pittsburgh

Jana Giceva, Technische Universität Munich Kartik Gopalan, Binghamton University

Redha Gouicem, *Technische Universität Munich* Xiaohui (Helen) Gu, *North Carolina State University*

Nastaran Hajinazar, Intel Labs

Kyle Hale, Illinois Institute of Technology

Niranjan Hasabnis, *Intel Labs* Chris Hawblitzel, *Microsoft Research* Michio Honda, *University of Edinburgh*

Liting Hu, Virginia Tech

Yu Hua, Huazhong University of Science and Technology

Călin Iorgulescu, Oracle Labs

Zsolt István, Technische Universität Darmstadt

Anand Iyer, Microsoft Research

Hani Jamjoom, IBM T. J. Watson Research

Yu Jiang, Tsinghua University

Myoungsoo Jung, Korea Advanced Institute of Science and Technology (KAIST)

Asim Kadav, Tonal

Vasiliki Kalavri, Boston University

Anuj Kalia, Microsoft

Sudarsun Kannan, Rutgers University

Sanidhya Kashyap, EPFL

Wook-Hee Kim, Konkuk University

Ricardo Koller, Google

Kenji Kono, Keio University

Youngjin Kwon, Korea Advanced Institute of Science and Technology (KAIST)

Sándor Laki, Eötvös Loránd University Michael Le, IBM T. J. Watson Research

Eunji Lee, Soongsil University

Baptiste Lepers, *Université de Neuchâtel* Alberto Lerner, *University of Fribourg* Yu Liang, *City University of Hong Kong*

Jean-Pierre Lozi, Inria

Youyou Lu, Tsinghua University

Xiaosong Ma, Qatar Computing Research Institute, Hamad Bin Khalifa University

Sarah Meiklejohn, University College London and Google

Mike Mesnier, *Intel Labs* Subrata Mitra, *Adobe Research*

Apoorve Mohan, IBM T. J. Watson Research Center

Amy L. Murphy, Bruno Kessler Foundation

Ruslan Nikolaev, The Pennsylvania State University

Pierre Olivier, The University of Manchester

Amy Ousterhout, University of California, San Diego

Yuvraj Patel, University of Edinburgh Fernando Pedone, University of Lugano Kevin Pedretti, Sandia National Laboratories Jan Rellermeyer, Leibniz University Hannover Larry Rudolph, Two Sigma Investments, LP

Leonid Ryzhyk, VMware Research

Russell Sears, Crystal DB

Mohammad Shahrad, University of British Columbia

Yizhou Shan, *Huawei Cloud* Liuba Shrira, *Brandeis University*

Georgios Smaragdakis, Delft University of Technology

Nik Sultana, *Illinois Institute of Technology* Cheng Tan, *Northeastern University* Vasily Tarasov, *IBM Research - Almaden*

Alain Tchana, ENSIMAG

Daniel R. Thomas, University of Strathclyde

Gaël Thomas, Télécom SudParis - Institut Polytechnique de Paris

Animesh Trivedi, Vrije Universiteit Amsterdam

Theodore Ts'o, Google

Chia-Che Tsai, Texas A&M University

Shay Vargaftik, VMware

Lluís Vilanova, Imperial College London Chen Wang, IBM T. J. Watson Research Center

Jason Waterman, Vassar College

Emmett Witchel, The University of Texas at Austin and Katana Graph

Youjip Won, Korea Advanced Institute of Science and Technology (KAIST)

Suzhen Wu, Xiamen University

Suli Yang, NetApp

Eiko Yoneki, University of Cambridge Feng Zhang, Tsinghua University Jie Zhang, Peking University Yongle Zhang, Purdue University Yuan Zhang, Fudan University Zheng Zhang, Rutgers University Yibo Zhu, ByteDance Inc.

#### **Steering Committee**

Irina Calciu, VMware Research Ada Gavrilovska, Georgia Institute of Technology Casey Henderson, USENIX Association Arvind Krishnamurthy, University of Washington Geoff Kuenning, Harvey Mudd College Brian Noble, *University of Michigan*Jiri Schindler, *Tranquil Data*Hakim Weatherspoon, *Cornell University*Erez Zadok, *Stony Brook University*Noa Zilberman, *University of Oxford*

## **External Reviewers**

Abhishek Bichhawat Dongsu Han Gilad Stern Adrian Perrig Giacomo Giuliari Daniel Cason Chun Jason Xue David Pointcheval Albert Cohen Kanak Mahadik

Ran Xu Ashraf Mahgoub Abraham Clements Kexin Pei

# Message from the USENIX ATC '23 Program Co-Chairs

#### Introduction

Welcome to the 2023 USENIX Annual Technical Conference (USENIX ATC '23). We are excited to be holding an inperson event with minimal visa issues requiring remote participation. Similar to last year, USENIX ATC '23 is co-located with OSDI. We very much look forward to meeting everyone in the systems community whether they attend USENIX ATC, OSDI, or both. The rest of this document provides some insights into the submission and selection process that culminated in 65 accepted works that will be presented at the conference.

#### **Submissions**

As in previous years, USENIX ATC '23 solicited three types of papers. In addition to full length, 11-page research papers, authors could submit 5-page short research papers that describe complete and properly evaluated ideas using fewer pages. Finally, to align with the USENIX mission of bringing together researchers in academia and systems practitioners, we continued the practice of soliciting papers describing the design, implementation, analysis, and experience with real-world deployment of systems and networks in a deployed systems track. These "Deployed Systems" papers had different criteria for acceptance from research papers, not needing to present new ideas or results to be accepted, but needing to convey practical insights.

A submission to USENIX ATC '23 involved more than a single PDF file. On the HotCRP submission system, each submission also contained an artifact description that included further details about the experimental environment. Optionally, authors could include a textual description of changes from previous submissions to help in the case where reviewers may have seen prior iterations of the paper while on other PCs. Finally, if on the deployed systems track, authors were required to specify a justification for why the paper belonged in that track.

#### **Program Committee Selection Process**

We assembled a program committee with many goals in mind: good coverage across diverse computer-systems topics, balance between academia and industry, a mix of veterans of prior USENIX ATC PCs with individuals in early stages of their professional careers, geographic diversity, and adherence to the USENIX diversity and inclusion principles. The assembled PC had 107 members from 19 countries, including 44% from North America, 33% from EMEA and 21% from APAC. 70% of the PC was from academia and 30% from industry, though some PC members from academia were also affiliated with industry. 55% of our PC were veteran PC members who had served USENIX ATC at least once in the past 4 years. Our PC had 26% female representation, which is higher than recent years (e.g., 18% for USENIX ATC '22). The main areas of expertise of PC members were Storage (24%), Distributed Systems (25%), Operating Systems (26%), Security (15%), Networking (12%), and Machine Learning (17%).

For the PC selection process, which was done well in advance of the submission deadline, we drew from a pool of experienced PC members who had served at least once in the prior 4 iterations of USENIX ATC, removing those who had served 4 times in a row and those who were concurrently serving for OSDI. In making our invitations, we prioritized several factors, including the following: reviewers flagged in HotCRP as producing good reviews for previous conferences; recommendations of researchers (usually early career) from invitees who were unable to serve; topic matches, trying to anticipate the need for Machine Learning expertise based on topic ratios from last year; and female representation, as it has been low in the USENIX ATC community.

During the review process, there were a few cases in which we needed expertise for a paper in which all reviewers identified low levels of expertise. For these, we solicited recommendations from the PC and invited external reviewers.

On January 9th, 2023, we held a synchronous online PC pre-review meeting to go over the unique aspects of USENIX ATC '23 submissions, and an overview of the duties and processes involving PC members, including bidding, reviewing rounds, online discussions, the author rebuttal, the PC meeting, and shepherding. Although attended by both veteran and new PC members, we hoped the meeting helped to welcome new PC members and provide opportunities for questions about the process. We held the meeting twice (7 hours apart) in an attempt to accommodate the various timezones of our international PC.

#### **Review Process**

USENIX ATC '23 received 353 submissions across all tracks, which was 10% fewer than USENIX ATC '22. Of these, 22 (6%) were deployed systems papers and 19 (5%) were short papers. The most popular topics for submissions, as specified by

authors were: Clouds, clusters, data centers (29%); ML/AI (24%); Storage, file systems (23%); Parallel and Distributed Systems (22%); Operating Systems, Kernels (14%); and Networking (14%).

We adopted a double-blind review process to minimize bias with strict anonymity rules. Four papers were ultimately rejected due to including author names, directly identifying or sharing a name or title with an existing technical report, or directly linking to a github repository under the author's name or institution. We identified one of these cases prior to reviewing, but the others were detected during the reviewing process.

We rejected three other submissions without review due to violations of the formatting guidelines, two papers for exceeding the length limits, and one that was too short and did not contain sufficient detail. Of particular note was the misuse of appendices, including very long appendices and appendices that contain information that is integral to the paper.

In order to increase the quality and relevance of reviews, we ran a bidding process in which PC members had 8 days to bid on which papers they felt were in their competency/expertise area and for which they could provide knowledgeable reviews. PC members also updated their topic preferences in HotCRP, which along with bid values were used by the HotCRP algorithm to assign papers. We took care to ensure that PC members requesting a lighter workload were assigned fewer papers in each round. Especially in the second round, we manually adjusted reviewers in cases where reviewer confidence was low, based mainly on PC members' bid values.

USENIX ATC '23 had two double-blind rounds of reviews. The goal of the first round was to identify early rejections and also identify for which papers the round 1 reviewers lacked sufficient expertise. In the first round we assigned 3 reviewers per paper, resulting in 1044 reviews. The reviewers had 5 weeks to review papers and 2 weeks for asynchronous online discussion. We notified authors of papers rejected in round 1 (216/353 = 61%) early (sent on March 22nd) to give these authors more time to prepare a future submission.

In the second round, we assigned at least two additional reviewers to the 132 submissions not rejected in round 1, amounting to 284 additional reviews, bringing the total number of reviews for round 2 papers to 5. The reviewers had 3.5 weeks to review these additional papers followed by 3 days of asynchronous online discussion to identify the most important questions for authors to respond to. Authors had 3 days to write a recommended 500 word response with a limit of 1000 words. Almost all authors wrote responses within this range. The reviewers continued the asynchronous online discussion for 1.5 weeks, converging to pre-accept, pre-reject, and pc-discussion decisions on papers. 48 papers were pre-accepted, leaving more discussion time for controversial papers at the synchronous virtual PC meeting. 37 papers were selected for discussion at the PC meeting, of which (22/37 = 59%) of papers were accepted.

We held a two-day synchronous virtual PC meeting with the goals of providing a high-bandwidth channel to resolve discussions, exposing all PC reviewers to a broader set of papers to level-set on quality, raising broader issues that may span multiple submissions and ultimately selecting the final program. We used Zoom, managing conflicts with breakout rooms and HotCRP to manage the discussion order. To manage timezones, we split the paper discussions into 2-hour blocks based on a Doodle poll of timezone availability for the specific reviewers on each paper. PC members were encouraged to attend all sessions regardless of whether one of their papers was being discussed. While it remains a challenge to have full PC participation for the entire meeting due to the wide range of timezones, we found the discussions to be lively and effective.

The PC selected 65 papers for an 18% acceptance rate. 11 were deployed systems papers, 3 were short, and the other 51 were full length research papers. Acceptance was based on the quality of the submissions; in-person conference constraints had no bearing on our decisions. After selecting the program, the program chairs selected two best papers based on nominations from the PC.

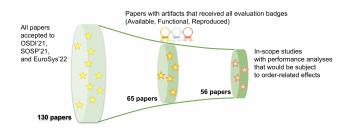

#### **Artifact Evaluation Process**

USENIX ATC '23 continued to run a joint artifact evaluation process with OSDI, led this year by Jianyu Jiang, Nathan Rutherford, and Cesar A. Stuardo. The artifact evaluation committee chairs assembled a committee consisting of 106 members. The authors of all accepted papers were invited to submit an artifact for an evaluation. 41 out of the 65 USENIX ATC papers (63%) did so. 98% of artifacts received an "Available" badge, 85% received a "Functional" badge, and 63% received a "Reproduced" badge. 61% of papers received all three badges (some artifacts were reproduced, but are not available).

Daniel Porto, researcher at INESC-ID in Lisbon, Portugal, passed away on April 29, 2023. He was a very talented and dedicated researcher, and a recognized expert in the areas of distributed systems and Byzantine consensus. His research led to several impactful publications in venues like EuroSys, OSDI, or DSN, and he served with a sense of community in several committees including the 2023 USENIX ATC/OSDI artifact evaluation committee. As a human being, Daniel will be remembered as an extraordinary person with an endless desire to help others. He touched the lives of many with his incredible generosity and kindness.

#### Acknowledgements

More than 200 people have contributed to the organization of the USENIX ATC '23, most of them in a voluntary capacity. We would like to thank each and every one of them. We are tremendously grateful to the program committee members for a job extremely well done, and for their personal sacrifices. We thank the Artifact Evaluation committee and the Artifact Evaluation Committee Chairs for their work and contribution, which improves our community and enables future research. Last, we thank the USENIX organization, the USENIX ATC steering committee and OSDI '23 co-chairs. The amount of work and preparation that goes into organizing a conference is immense, and we were astounded by the help and support provided by everyone involved.

Julia Lawall, *Inria*Dan Williams, *Virginia Tech*USENIX ATC '23 Program Co-Chairs

# 2023 USENIX Annual Technical Conference July 10–12, 2023 Boston, MA, USA

## Monday, July 10

| Security and Privacy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bifrost: Analysis and Optimization of Network I/O Tax in Confidential Virtual Machines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SecretFlow-SPU: A Performant and User-Friendly Framework for Privacy-Preserving Machine Learning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Portunus: Re-imagining Access Control in Distributed Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Searching Graphs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| GLogS: Interactive Graph Pattern Matching Query At Large Scale                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

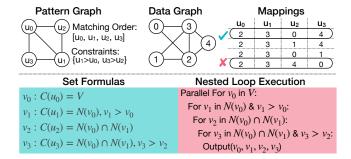

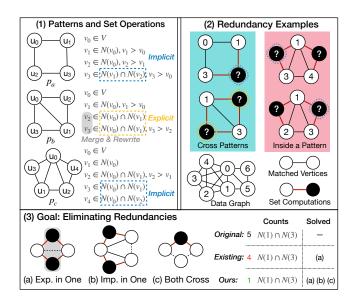

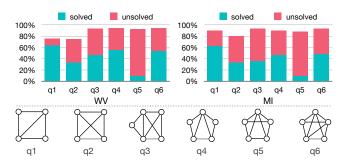

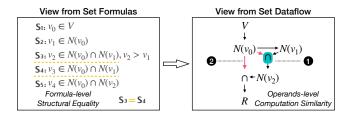

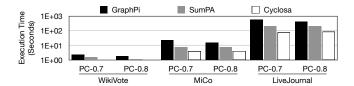

| Cyclosa: Redundancy-Free Graph Pattern Mining via Set Dataflow.  Chuangyi Gui, National Engineering Research Center for Big Data Technology and System/Service Computing Technology and System Lab/Cluster and Grid Computing Lab, Huazhong University of Science and Technology, China; Zhejiang Lab, China; Xiaofei Liao, National Engineering Research Center for Big Data Technology and System/Service Computing Technology and System Lab/Cluster and Grid Computing Lab, Huazhong University of Science and Technology, China; Long Zheng, National Engineering Research Center for Big Data Technology and System/Service Computing Technology and System Lab/Cluster and Grid Computing Lab, Huazhong University of Science and Technology, China; Zhejiang Lab, China; Hai Jin, National Engineering Research Center for Big Data Technology and System/Service Computing Technology and System Lab/Cluster and Grid Computing Lab, Huazhong University of Science and Technology, China |

| SOWalker: An I/O-Optimized Out-of-Core Graph Processing System for Second-Order Random Walks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Yutong Wu, Zhan Shi, Shicai Huang, Zhipeng Tian, Pengwei Zuo, Peng Fang, Fang Wang, and Dan Feng, Wuhan National Laboratory for Optoelectronics Huazhong University of Science and Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Deduplication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <b>Light-Dedup: A Light-weight Inline Deduplication Framework for Non-Volatile Memory File Systems</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TiDedup: A New Distributed Deduplication Architecture for Ceph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| LoopDelta: Embedding Locality-aware Opportunistic Delta Compression in Inline Deduplication for Highly Efficient Data Reduction                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Yucheng Zhang, School of Mathematics and Computer Sciences, Nanchang University and Wuhan National Laboratory for Optoelectronics, Huazhong University of Science and Technology; Hong Jiang, Department of Computer Science and Engineering, University of Texas at Arlington; Dan Feng, Wuhan National Laboratory for Optoelectronics, Huazhong University of Science and Technology; Nan Jiang, School of Information Engineering, East China Jiaotong University; Taorong Qiu and Wei Huang, School of Mathematics and Computer Sciences, Nanchang University |

| Structuring Graphs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TC-GNN: Bridging Sparse GNN Computation and Dense Tensor Cores on GPUs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Legion: Automatically Pushing the Envelope of Multi-GPU System for Billion-Scale GNN Training                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

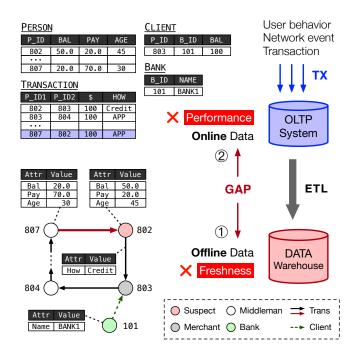

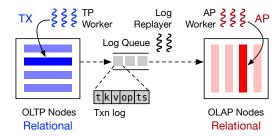

| Bridging the Gap between Relational OLTP and Graph-based OLAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Placement and Fault Tolerance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

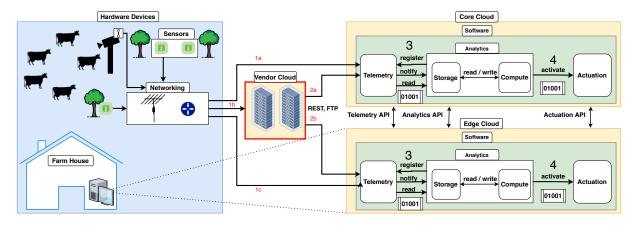

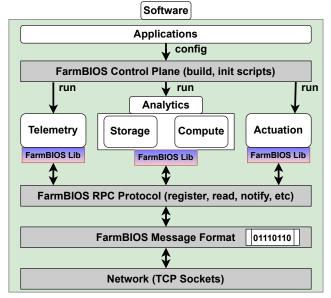

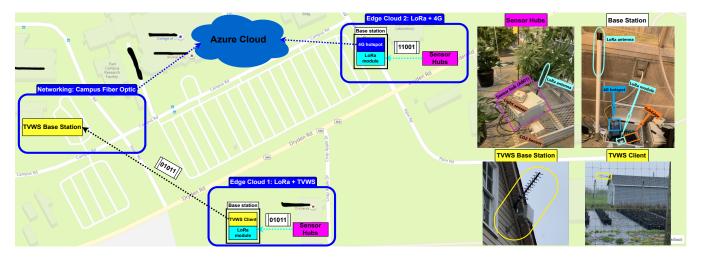

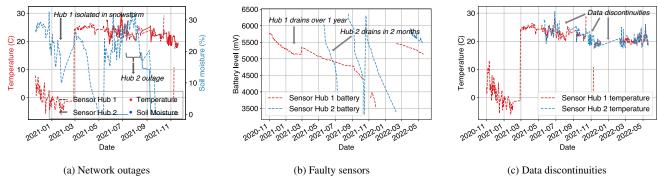

| Comosum: An Extensible, Reconfigurable, and Fault-Tolerant IoT Platform for Digital Agriculture                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

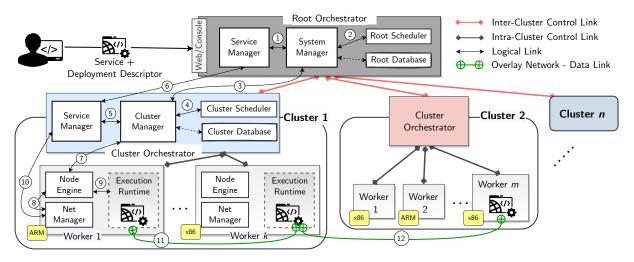

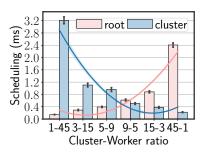

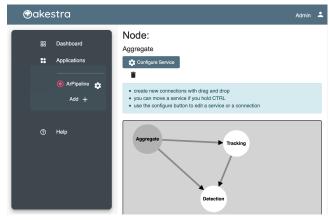

| Oakestra: A Lightweight Hierarchical Orchestration Framework for Edge Computing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

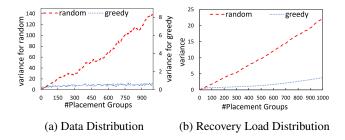

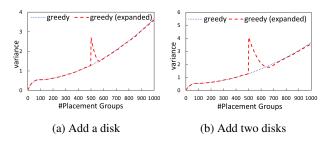

| Explore Data Placement Algorithm for Balanced Recovery Load Distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| <b>Updating Code</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

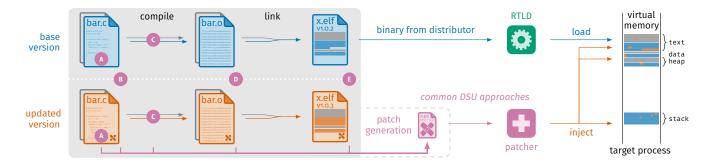

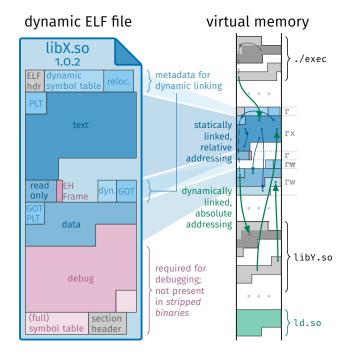

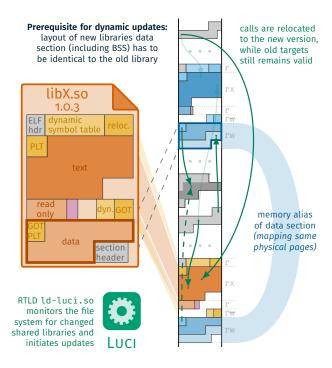

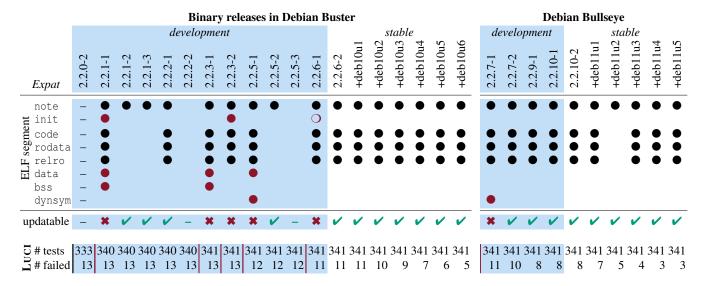

| Luci: Loader-based Dynamic Software Updates for Off-the-shelf Shared Objects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

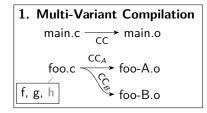

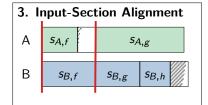

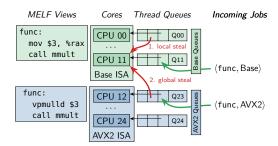

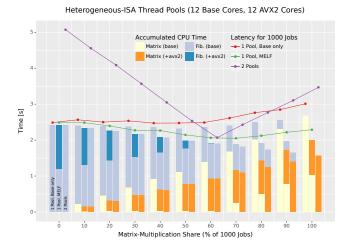

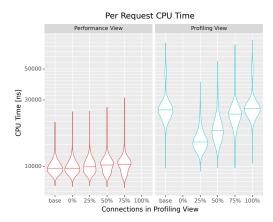

| <b>MELF: Multivariant Executables for a Heterogeneous World</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

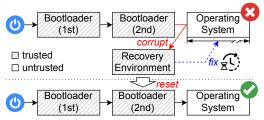

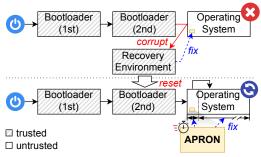

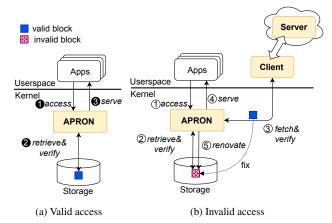

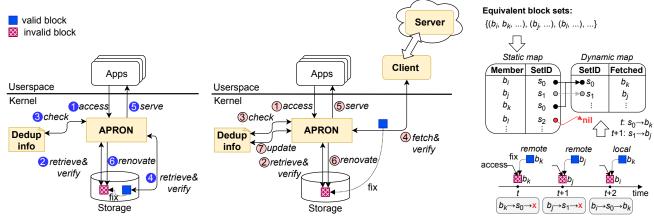

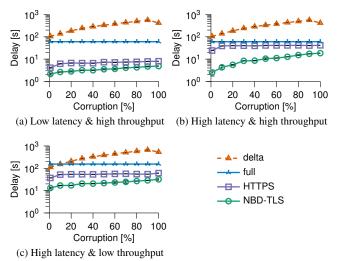

| APRON: Authenticated and Progressive System Image Renovation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

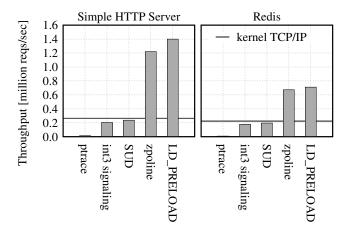

| <b>zpoline: a system call hook mechanism based on binary rewriting</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

# Tuesday, July 11

| Serverless                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

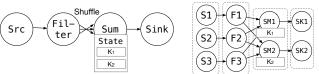

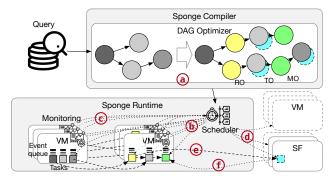

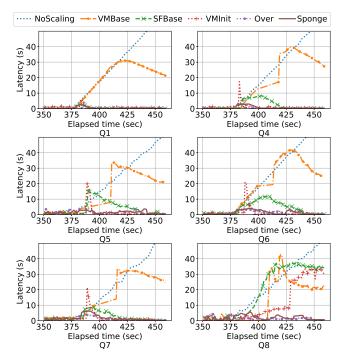

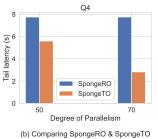

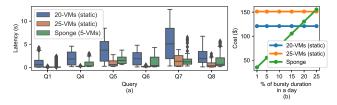

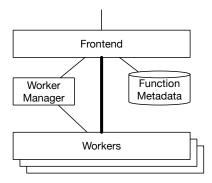

| Sponge: Fast Reactive Scaling for Stream Processing with Serverless Frameworks                                                                                                                                                                                                                                                                                                                          |

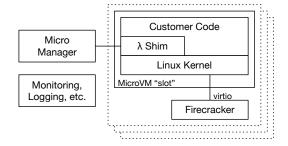

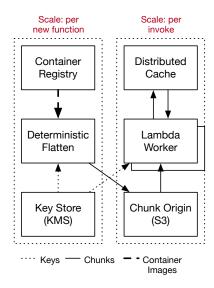

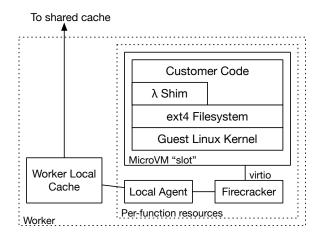

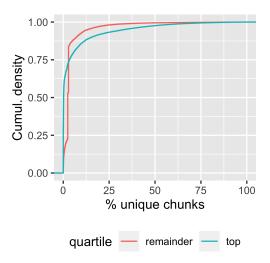

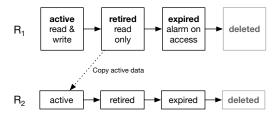

| On-demand Container Loading in AWS Lambda. 318 Marc Brooker, Mike Danilov, Chris Greenwood, and Phil Piwonka, Amazon Web Services                                                                                                                                                                                                                                                                       |

| Decentralized and Stateful Serverless Computing on the Internet Computer Blockchain                                                                                                                                                                                                                                                                                                                     |

| Troubleshooting and Measurement                                                                                                                                                                                                                                                                                                                                                                         |

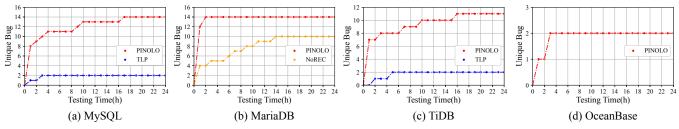

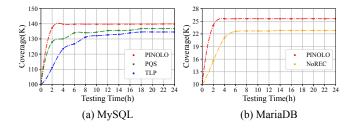

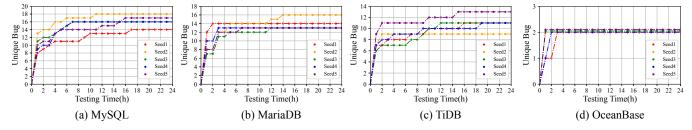

| Pinolo: Detecting Logical Bugs in Database Management Systems with Approximate Query Synthesis                                                                                                                                                                                                                                                                                                          |

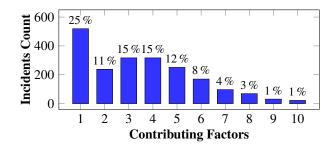

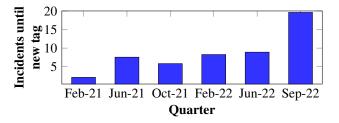

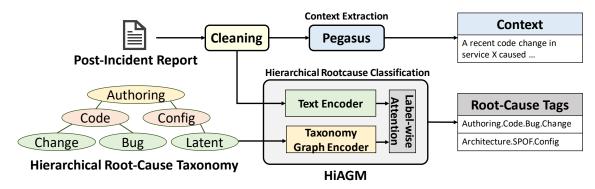

| AutoARTS: Taxonomy, Insights and Tools for Root Cause Labelling of Incidents in Microsoft Azure                                                                                                                                                                                                                                                                                                         |

| Avoiding the Ordering Trap in Systems Performance Measurement                                                                                                                                                                                                                                                                                                                                           |

| Cloud and Microservices                                                                                                                                                                                                                                                                                                                                                                                 |

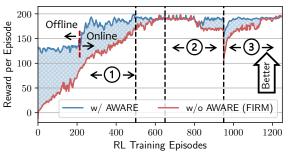

| AWARE: Automate Workload Autoscaling with Reinforcement Learning in Production Cloud Systems 387. Haoran Qiu and Weichao Mao, <i>University of Illinois at Urbana-Champaign;</i> Chen Wang, Hubertus Franke, and Alaa Youssef, <i>IBM Research;</i> Zbigniew T. Kalbarczyk, Tamer Başar, and Ravishankar K. Iyer, <i>University of Illinois at Urbana-Champaign</i>                                     |

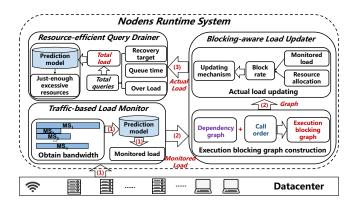

| Nodens: Enabling Resource Efficient and Fast QoS Recovery of Dynamic Microservice Applications in Datacenters 403 Jiuchen Shi, Hang Zhang, Zhixin Tong, Quan Chen, Kaihua Fu, and Minyi Guo, Department of Computer Science and Engineering, Shanghai Jiao Tong University                                                                                                                              |

| Lifting the veil on Meta's microservice architecture: Analyses of topology and request workflows                                                                                                                                                                                                                                                                                                        |

| Distributed Storage                                                                                                                                                                                                                                                                                                                                                                                     |

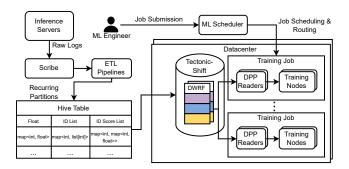

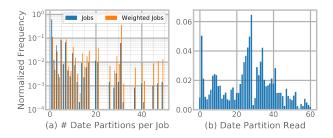

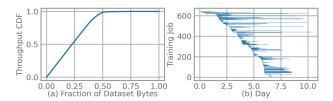

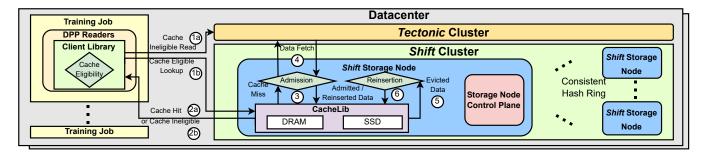

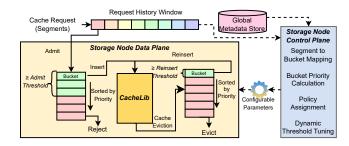

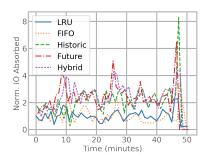

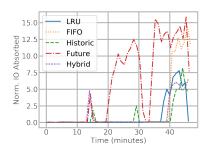

| Tectonic-Shift: A Composite Storage Fabric for Large-Scale ML Training. 433 Mark Zhao, Stanford University and Meta; Satadru Pan, Niket Agarwal, Zhaoduo Wen, David Xu, Anand Natarajan, Pavan Kumar, Shiva Shankar P, Ritesh Tijoriwala, Karan Asher, Hao Wu, Aarti Basant, Daniel Ford, Delia David, Nezih Yigitbasi, Pratap Singh, and Carole-Jean Wu, Meta; Christos Kozyrakis, Stanford University |

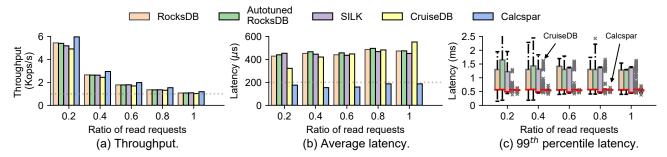

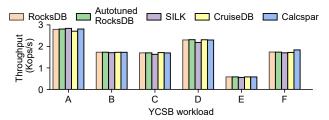

| Calcspar: A Contract-Aware LSM Store for Cloud Storage with Low Latency Spikes                                                                                                                                                                                                                                                                                                                          |

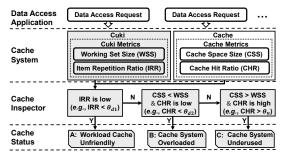

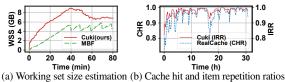

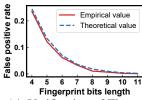

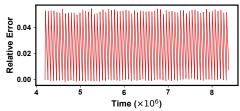

| Adaptive Online Cache Capacity Optimization via Lightweight Working Set Size Estimation at Scale                                                                                                                                                                                                                                                                                                        |

| Hardware and Software for Security and Performance                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------|

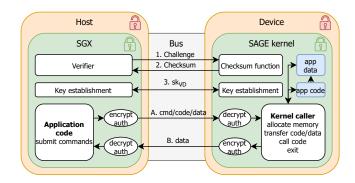

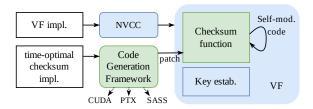

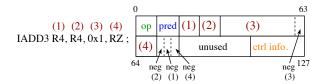

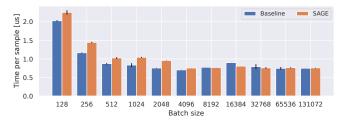

| SAGE: Software-based Attestation for GPU Execution                                                                                    |

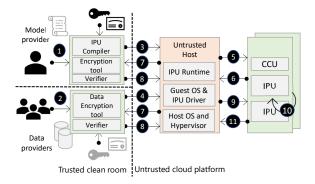

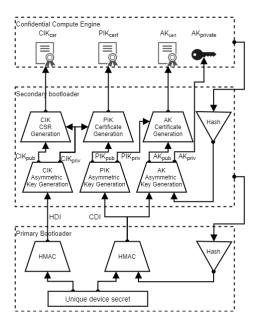

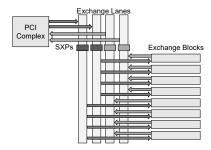

| Confidential Computing within an AI Accelerator                                                                                       |

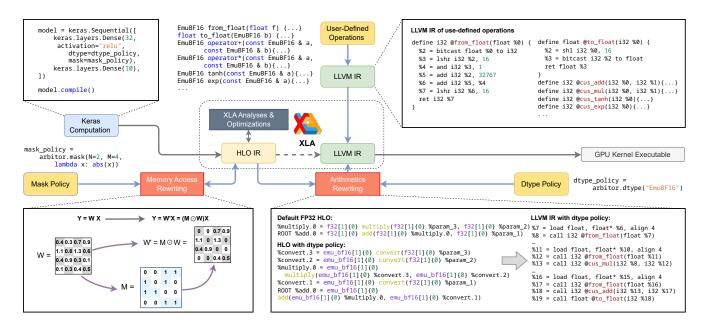

| Arbitor: A Numerically Accurate Hardware Emulation Tool for DNN Accelerators                                                          |

| Networking                                                                                                                            |

| bBBR: Optimize Retransmissions of BBR Flows on the Internet                                                                           |

| Bridging the Gap between QoE and QoS in Congestion Control: A Large-scale Mobile Web Service Perspective                              |

| FarReach: Write-back Caching in Programmable Switches                                                                                 |

| Memory-Related Hardware and Software                                                                                                  |

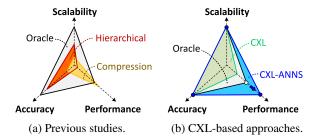

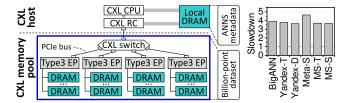

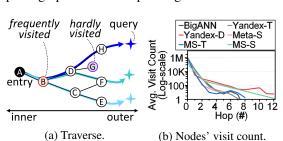

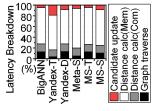

| CXL-ANNS: Software-Hardware Collaborative Memory Disaggregation and Computation for Billion-Scale Approximate Nearest Neighbor Search |

| Overcoming the Memory Wall with CXL-Enabled SSDs                                                                                      |

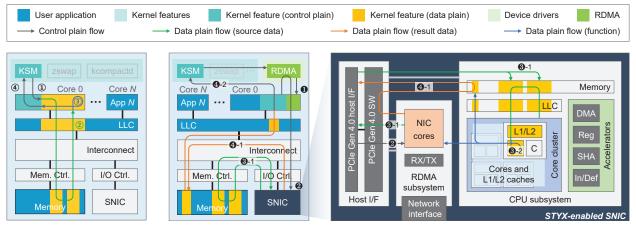

| Styx: Exploiting SmartNIC Capability to Reduce Datacenter Memory Tax                                                                  |

| Deployed Networking                                                                                                                   |

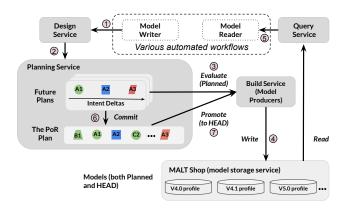

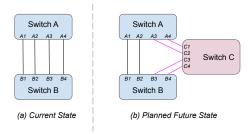

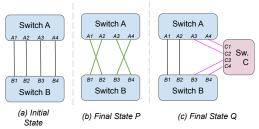

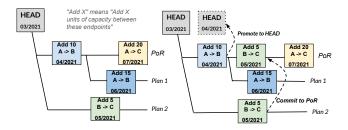

| Change Management in Physical Network Lifecycle Automation                                                                            |

| AAsclepius: Monitoring, Diagnosing, and Detouring at the Internet Peering Edge                                                                                                                                                                                                          | 55        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

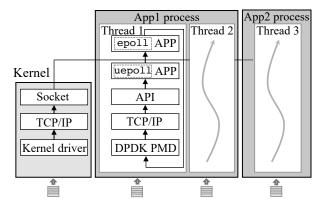

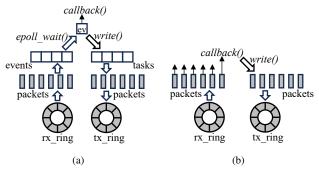

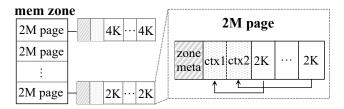

| Deploying User-space TCP at Cloud Scale with Luna. 67.  Lingjun Zhu, Yifan Shen, Erci Xu, Bo Shi, Ting Fu, Shu Ma, Shuguang Chen, Zhongyu Wang, Haonan Wu, Xingyu Liao, Zhendan Yang, Zhongqing Chen, Wei Lin, Yijun Hou, Rong Liu, Chao Shi, Jiaji Zhu, and Jiesheng Wu, Alibaba Group | 73        |

| Key-Value Stores                                                                                                                                                                                                                                                                        |           |

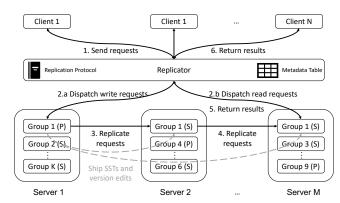

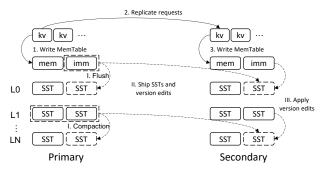

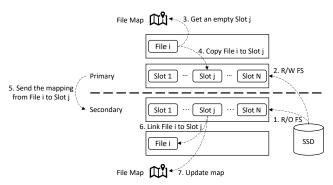

| RubbleDB: CPU-Efficient Replication with NVMe-oF. 68 Haoyu Li, Sheng Jiang, and Chen Chen, Columbia University; Ashwini Raina, Princeton University; Xingyu Zhu, Changxu Luo, and Asaf Cidon, Columbia University                                                                       | 89        |

| Distributed Transactions at Scale in Amazon DynamoDB                                                                                                                                                                                                                                    | 05        |

| Security: Attacks                                                                                                                                                                                                                                                                       |           |

| Prefix Siphoning: Exploiting LSM-Tree Range Filters For Information Disclosure                                                                                                                                                                                                          | 19        |

| EPF: Evil Packet Filter                                                                                                                                                                                                                                                                 | 35        |

| Wednesday, July 12                                                                                                                                                                                                                                                                      |           |

| Virtual Machines                                                                                                                                                                                                                                                                        |           |

| Translation Pass-Through for Near-Native Paging Performance in VMs                                                                                                                                                                                                                      |           |

| Efficient Memory Overcommitment for I/O Passthrough Enabled VMs via Fine-grained Page Meta-data                                                                                                                                                                                         |           |

| Management                                                                                                                                                                                                                                                                              | 69        |

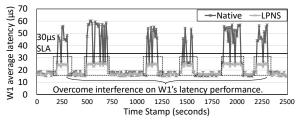

| <b>LPNS: Scalable and Latency-Predictable Local Storage Virtualization for Unpredictable NVMe SSDs in Clouds 78</b> Bo Peng, Cheng Guo, Jianguo Yao, and Haibing Guan, <i>Shanghai Jiao Tong University</i>                                                                             | 85        |

| Persistent Memory                                                                                                                                                                                                                                                                       |           |

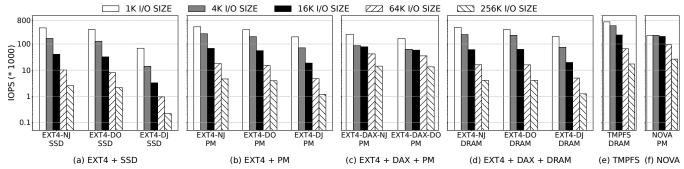

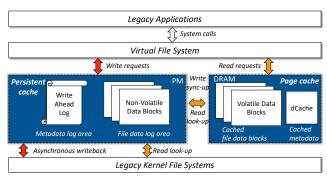

| P <sup>2</sup> Cache: Exploring Tiered Memory for In-Kernel File Systems Caching                                                                                                                                                                                                        | 01        |

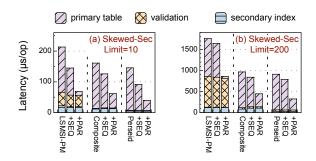

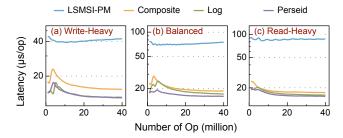

| Revisiting Secondary Indexing in LSM-based Storage Systems with Persistent Memory                                                                                                                                                                                                       | <b>17</b> |

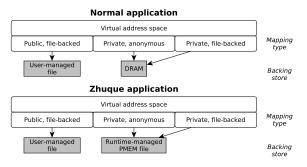

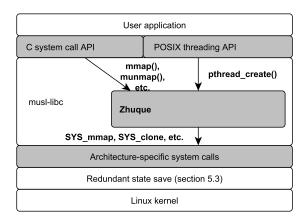

| Zhuque: Failure is Not an Option, it's an Exception                                                                                                                                                                                                                                     | 33        |

| Offloading and Scheduling                                                                                                                                                                                                                                                                                                                                                              |                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

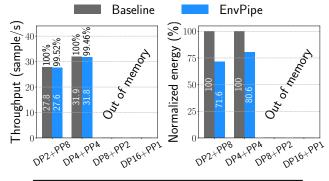

| EnvPipe: Performance-preserving DNN Training Framework for Saving Energy                                                                                                                                                                                                                                                                                                               | 51                              |

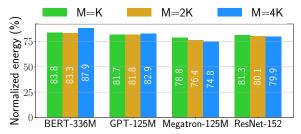

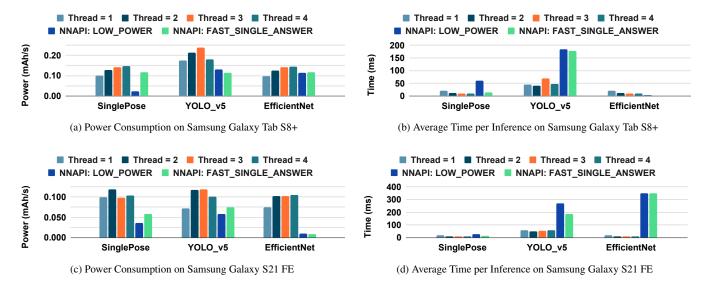

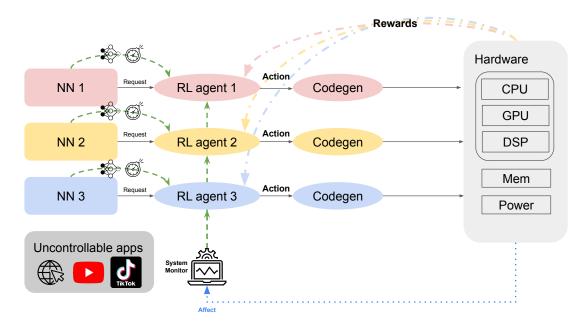

| Decentralized Application-Level Adaptive Scheduling for Multi-Instance DNNs on Open Mobile Devices 80 Hsin-Hsuan Sung and Jou-An Chen, Department of Computer Science, North Carolina State University; Wei Niu, Jiexiong Guan, and Bin Ren, Department of Computer Science, William & Mary; Xipeng Shen, Department of Computer Science, North Carolina State University              | 65                              |

| UnFaaSener: Latency and Cost Aware Offloading of Functions from Serverless Platforms                                                                                                                                                                                                                                                                                                   | <b>79</b>                       |

| Kernel and Concurrency                                                                                                                                                                                                                                                                                                                                                                 |                                 |

| LLFREE: Scalable and Optionally-Persistent Page-Frame Allocation                                                                                                                                                                                                                                                                                                                       | 97                              |

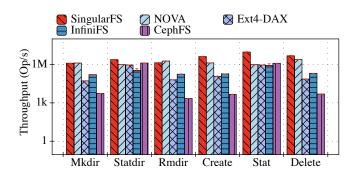

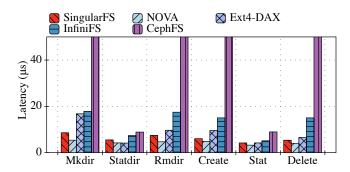

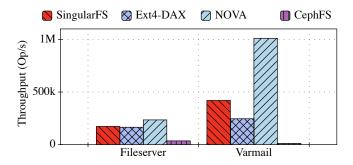

| SINGULARFS: A Billion-Scale Distributed File System Using a Single Metadata Server                                                                                                                                                                                                                                                                                                     | 15                              |

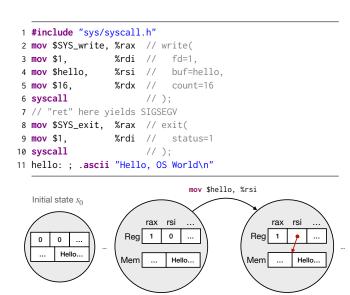

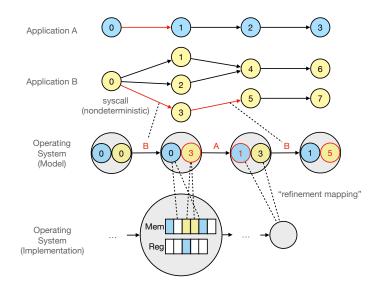

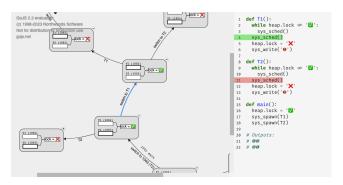

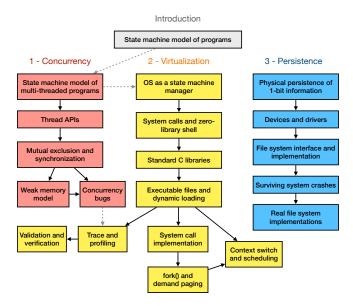

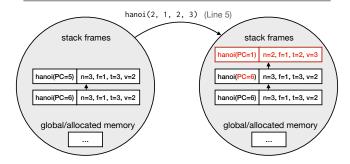

| The Hitchhiker's Guide to Operating Systems                                                                                                                                                                                                                                                                                                                                            | 29                              |

| Optimizing ML                                                                                                                                                                                                                                                                                                                                                                          |                                 |

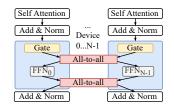

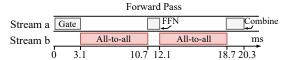

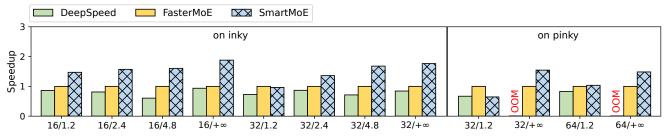

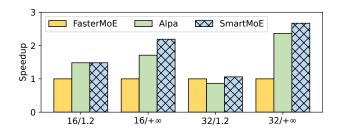

| Accelerating Distributed MoE Training and Inference with Lina                                                                                                                                                                                                                                                                                                                          | 45                              |

| SMARTMoE: Efficiently Training Sparsely-Activated Models through Combining Offline and Online Parallelization 9 Mingshu Zhai, Jiaao He, Zixuan Ma, Zan Zong, Runqing Zhang, and Jidong Zhai, <i>Tsinghua University</i>                                                                                                                                                                | 61                              |

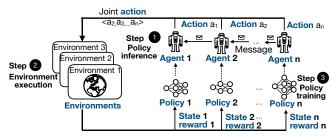

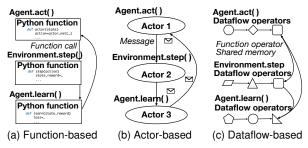

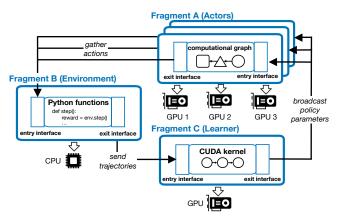

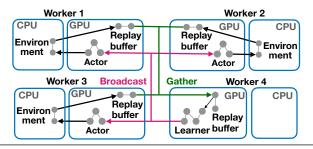

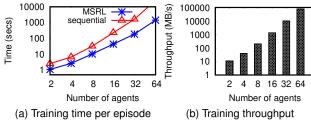

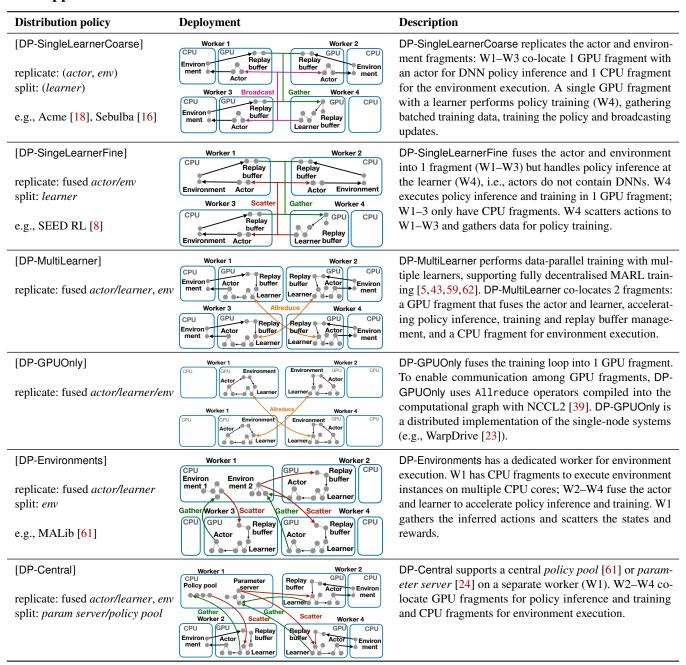

| MSRL: Distributed Reinforcement Learning with Dataflow Fragments.  Huanzhou Zhu, Imperial College London; Bo Zhao, Imperial College London and Aalto University; Gang Chen, Weifeng Chen, Yijie Chen, and Liang Shi, Huawei Technologies Co., Ltd.; Yaodong Yang, Peking University; Peter Pietzuch, Imperial College London; Lei Chen, Hong Kong University of Science and Technology | 77                              |

| GPU                                                                                                                                                                                                                                                                                                                                                                                    |                                 |

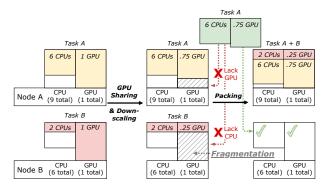

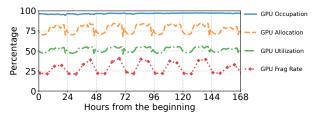

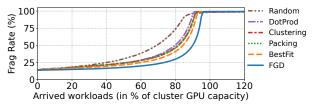

| Beware of Fragmentation: Scheduling GPU-Sharing Workloads with Fragmentation Gradient Descent                                                                                                                                                                                                                                                                                          | 95                              |

| Towards Iterative Relational Algebra on the GPU                                                                                                                                                                                                                                                                                                                                        | 09                              |

| <b>VectorVisor: A Binary Translation Scheme for Throughput-Oriented GPU Acceleration</b>                                                                                                                                                                                                                                                                                               | 17                              |

| LLFREE: Scalable and Optionally-Persistent Page-Frame Allocation                                                                                                                                                                                                                                                                                                                       | 015<br>029<br>045<br>061<br>077 |

## Bifrost: Analysis and Optimization of Network I/O Tax in Confidential Virtual Machines

Dingji Li<sup>1,2,3</sup>, Zeyu Mi<sup>1,2</sup>, Chenhui Ji<sup>1,2</sup>, Yifan Tan<sup>1,2</sup>, Binyu Zang<sup>1,2</sup>, Haibing Guan<sup>4</sup>, and Haibo Chen<sup>1,2</sup>

<sup>1</sup>Institute of Parallel and Distributed Systems, SEIEE, Shanghai Jiao Tong University

<sup>2</sup>Engineering Research Center for Domain-specific Operating Systems, Ministry of Education, China

<sup>3</sup>MoE Key Lab of Artificial Intelligence, AI Institute, Shanghai Jiao Tong University

<sup>4</sup>Shanghai Key Laboratory of Scalable Computing and Systems, Shanghai Jiao Tong University

#### **Abstract**

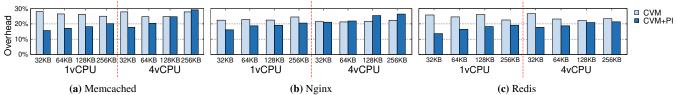

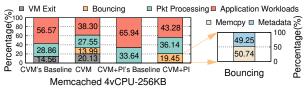

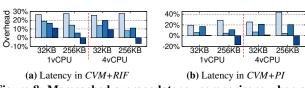

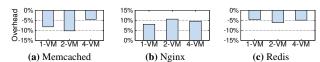

Existing confidential VMs (CVMs) experience notable network performance overhead compared to traditional VMs. We present the first thorough performance analysis of various network-intensive applications in CVMs and find that the CVM-IO tax, which mainly comprises the bounce buffer mechanism and the packet processing in CVMs, has a significant impact on network I/O performance. Specifically, the CVM-IO tax squeezes out virtual CPU (vCPU) resources of performance-critical application workloads and may occupy more than 50% of CPU cycles. To minimize the CVM-IO tax, this paper proposes Bifrost, a novel para-virtualized I/O design that 1) eliminates the I/O payload bouncing tax by removing redundant encryption and 2) reduces the packet processing tax via pre-receiver packet reassembly, while still ensuring the same level of security guarantees. We have implemented a Bifrost prototype with only minor modifications to the guest Linux kernel and the userspace network I/O backend. Evaluation results on both AMD and Intel servers demonstrate that Bifrost significantly improves the performance of I/Ointensive applications in CVMs, and even outperforms the traditional VM by up to 21.50%.

#### 1 Introduction

As more and more data-processing applications [9, 13, 14, 57] embrace the cloud, widespread concerns are being raised about the security and privacy of data in-use on the cloud. To address these concerns, various confidential computing solutions have been proposed to safeguard data from unauthorized parties. Among them, confidential virtual machine (CVM) solutions, such as AMD SEV [2, 3], Intel TDX [32] and ARM CCA [8], run guest operating systems (OSes) in hardware-isolated environments. In these environments, the complex virtualization stack, such as hypervisor and host OS, is no longer trusted and cannot access data in guest OSes arbitrarily, while still providing resource management functions. This CVM abstraction transparently protects user workloads without requiring any modifications and integrates easily into

the existing cloud infrastructure. Therefore, it has gained popularity and is increasingly deployed in data centers.

Unfortunately, while the speed of modern network devices continues to grow (Terabit Ethernet [60] like NVIDIA 400Gbps NIC [51]), the security protections introduced by existing CVM solutions have a significant negative impact on network performance. This paper first conducts a series of experiments to thoroughly analyze the network I/O performance of CVMs. We evaluate widely-deployed network-intensive applications in an AMD SEV-ES/SNP server and a simulated Intel TDX server. The results demonstrate that CVM's security protections significantly increase the CVM-IO tax, which we define as the CPU resources used during CVM's I/O procedure, resulting in up to 29% overhead over a traditional VM that does not use any CVM protections. The CVM-IO tax is caused by both security protections and intrinsic network I/O procedures in CVMs, draining substantial CPU resources from diverse application workloads.

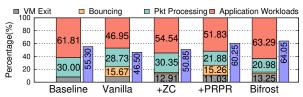

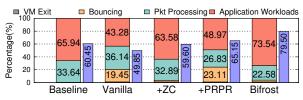

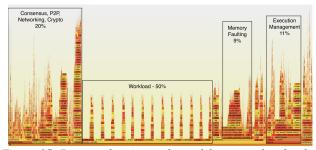

Concretely, there are three common components in the CVM-IO tax: ① VM exits consume up to 11.54% more CPU cycles than the traditional VM. The time consumption of VM exits is greatly increased due to the security checks and protections from the trusted modules (e.g., AMD-SP [3], Intel TDX module [31]) and making the guest aware of emulation events (e.g., AMD #VC [3], Intel #VE [29]). ② The bounce buffer mechanism, an I/O staging memory shared between the CVM and hypervisor, takes up to 19.45% CPU cycles for bouncing packets (including headers and payload). I/O operations that could previously be done directly by the hypervisor to the traditional VMs must now be assisted by the bounce buffer mechanism in guest OSes. For example, to emulate a virtual NIC, the hypervisor in traditional VM systems can forward packets between the guest OS and the host network stack by directly copying I/O data to/from the guest private memory. But hypervisors in CVM systems require the guest OS to bounce packets to/from a hypervisor-visible shared memory region due to the memory encryption, introducing I/O data copy overhead. 3 The packet processing also spends up to 36.14% CPU cycles preparing payloads from massive network packets for application workloads. The

<sup>&</sup>lt;sup>™</sup>Corresponding author: Zeyu Mi (yzmizeyu@sjtu.edu.cn).

higher the number of packets transferred to the network stack, the more vCPU resources a CVM requires to process their headers. Fortunately, the cost of VM exits becomes negligible when the posted interrupt [59] feature is supported by the hardware, leaving the bounce buffer mechanism and packet processing as the main components of the CVM-IO tax.

This paper aims to **reduce as much CVM-IO tax as possible** for I/O-intensive applications in CVMs by bypassing the bounce buffer mechanism and offloading the packet processing. A straightforward design to bypass the bounce buffer mechanism is to keep the packet content in place by dynamically adjusting the accessibility of the same memory region to the hypervisor. However, this approach is limited by the memory encryption hardware support [34], which does not allow the plaintext contents of a memory region to be preserved when modifying the accessibility of the memory region [29]. To reduce network packet processing cost, the existing design is to pass fewer packets to the network stack by reassembling multiple small packets into a large one in the guest device driver. But the guest device driver still has to process a large number of packets, consuming substantial CPU resources.

Fortunately, there are three observations that can help us address the challenges mentioned above. We observe that either end-to-end encryption or a CVM's private memory alone can protect data security, while applying both protections to the payload is redundant. Additionally, we notice that end-to-end encryption/decryption can also change the payload's memory location, which is functionally equivalent to bouncing between two memory regions. As a result, bypassing payload bouncing can be achieved by directly encrypting/decrypting the payload into/from the guest-host shared memory. Another observation is that the network I/O backend typically has plenty of residual CPU resources. Given the bottleneck experienced by the saturated vCPUs of network-intensive CVMs, an opportunity arises to offload packet processing to the network I/O backend. This approach effectively utilizes the available CPU resources, alleviating the strain on vCPUs and resulting in improved performance.

Based on these observations, this paper proposes **Bifrost**<sup>1</sup> to improve the paravirtual network performance of the CVM with three techniques: ① The *zero-copy encryption deduplication* eliminates payload bouncing by leveraging dedicated guest-host shared memory to remove redundant encryptions on the payload in a zero-copy way. When receiving packets, the end-to-end encrypted payload is directly decrypted from the shared memory. When sending packets, the payload is directly encrypted into the shared memory. To minimize modifications, the shared memory is in the form of dedicated non-uniform memory access (NUMA) [37] nodes, allowing memory allocators in the guest kernel to be reused. ② The *one-time trusted read* mechanism protects guest OSes from time

of check to time of use (TOCTTOU) attacks while accessing packets in the dedicated shared memory. With these two techniques, the bouncing of the end-to-end encrypted payload, which takes up much CPU resources of CVMs, is securely bypassed. ③ The *pre-receiver packet reassembly* reduces vCPU resources utilized by the device driver by offloading the task of reassembling received packets to the network I/O backend. Thus, CVMs are able to process fewer packets with larger payload, reducing the packet processing cost on vCPUs.

We have implemented a Bifrost prototype by modifying the guest OS kernel and host user-level software. The prototype extends the Linux v6.0-rc1 kernel in the guest OS with 815 lines of code, and adds 175 lines to OpenvSwitch v2.17.3 and 541 lines to DPDK v21.1.2, both of which run in the host user mode. We have also evaluated Bifrost's performance on both AMD and Intel platforms. The results show that, with advanced posted interrupt support, Bifrost enhances the performance of I/O-intensive applications in CVMs, surpassing traditional VMs by up to 21.50%.

In summary, this paper makes the following contributions:

- The first thorough performance analysis of I/O-intensive applications in CVMs on existing and next-generation hardware platforms, revealing their bottlenecks and overhead sources compared to traditional VMs.

- A secure paravirtual I/O design that greatly reduces the CVM-IO tax, significantly improving the performance of I/O-intensive applications in CVMs.

- A Bifrost prototype and a comprehensive evaluation on AMD and Intel platforms, demonstrating improvements on existing and future CVM hardware. The prototype is available at https://github.com/IPADS-Bifrost.

#### 2 Background

#### 2.1 Confidential VMs (CVMs)

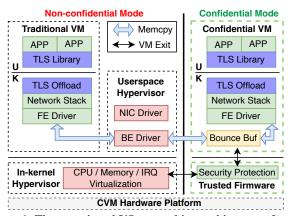

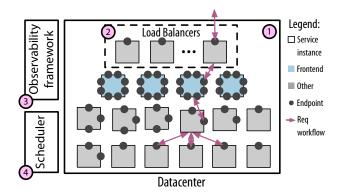

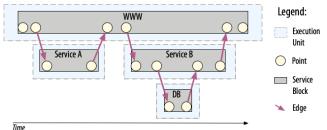

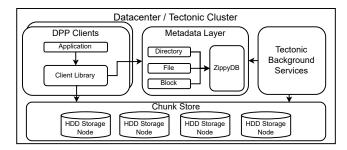

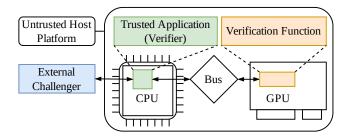

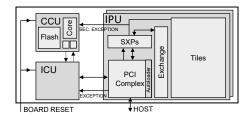

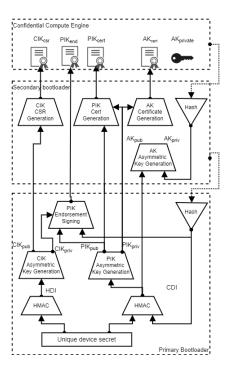

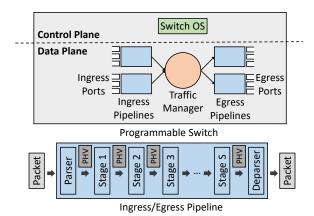

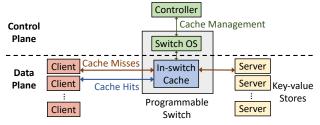

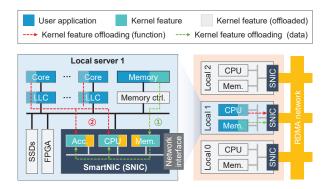

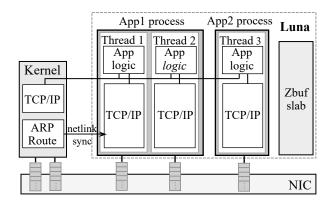

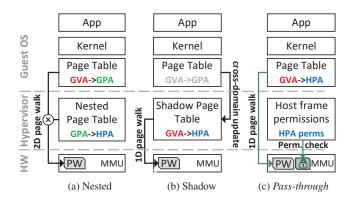

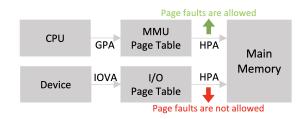

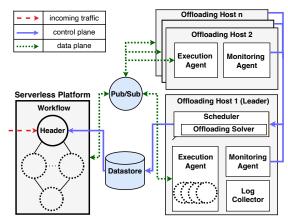

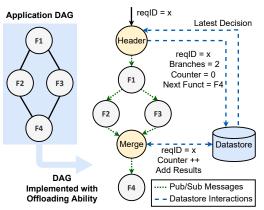

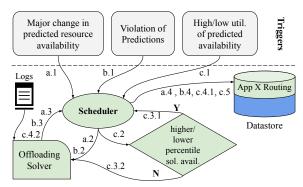

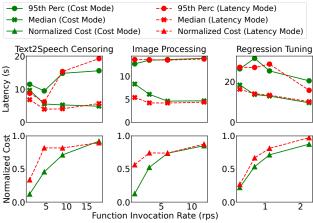

There are different CVM solutions based on specialized hardware extensions. All of these solutions leverage hardware memory encryption and integrity checking [30, 34] to enforce confidentiality and integrity. They share the same CVM abstraction that excludes the entire virtualization stack from the trusted computing base (TCB). As shown in Figure 1, the trusted firmware, which is the unique software TCB, isolates the CVM from untrusted hypervisors and traditional VMs.

Existing CVM systems typically divide the physical memory of a VM into two major security types: private memory and shared memory. The private memory is encrypted by hardware and cannot be accessed or modified by any untrusted entities outside the VM, while the shared memory holding plaintext data can be accessed by the hypervisor. The CVM systems also allow the hypervisor to switch private memory and shared memory to each other at runtime. However, the data content of the memory page cannot be preserved before and after the security type switch [29]. Hence, the guest must

<sup>&</sup>lt;sup>1</sup>Bifrost, the rainbow bridge from Norse mythology, metaphorically represents the secure and rapid transfer of CVM's I/O data (Asgard's gods) to and from the untrusted hypervisor (Midgard).

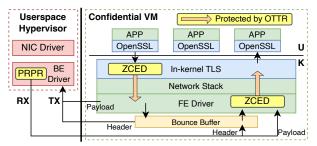

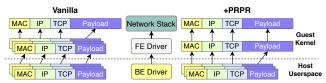

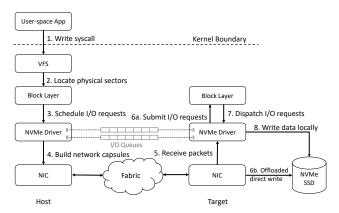

Figure 1: The paravirtual I/O networking architecture of traditional VMs and CVMs atop the CVM hardware platform. The black arrows represent the path of VM exits and VM enters. The light blue arrows indicate memory copies that consume CPU resources. The FE Driver and the BE Driver in the figure represent drivers in frontend and backend, respectively.

move data outside of private memory before the security type switch, and then copy it back to the new shared memory. Besides, it takes much effort to finish the security type switch. The guest OS has to cooperate with the host hypervisor to alter address translation data structures and maintain CPU micro-architectures, requiring multiple VM exits and interprocessor communications [4, 29]. As a result, the security type switch is unsuitable to occur frequently in CVMs.

#### 2.2 Paravirtual I/O Networking in CVM

Paravirtual I/O has become a primary I/O virtualization choice for modern cloud providers owing to its high performance and excellent compatibility. There are two cooperative drivers in paravirtual I/O, a frontend driver in the guest VM and a backend driver in the hypervisor, which communicate with each other through shared memory. To provide maximum network performance, the backend driver can be deployed in the host userspace, for instance, using vhost-user [46,53], to directly control the device in a busy-polling mode [16].

An example of paravirtual I/O networking of the traditional VM is shown in the left part of Figure 1. The applications in the userspace deal with payload, while the network stack and the frontend driver in the kernel handle packet processing. The packet processing includes network functions that handle conversions between payload and packets. For example, in the transmission (TX) direction, the payload from applications and the headers from the network stack are encapsulated into network packets, after which the backend driver is notified to send them out. Because the hypervisor can access the entire memory space of a traditional VM, the backend driver can copy the packets freely from the guest memory to its own memory and forwards them to the NIC driver.

Memory pages in CVMs, including those containing packets, are set to private by default. However, the host OS is untrusted and cannot access the private memory of CVMs

(see § 2.1). To allow the host OS to transfer packets, CVMs utilize a bounce buffer mechanism that sets up a guest-host shared memory as an intermediary. As shown in the right part of Figure 1, the guest OS reserves a shared memory region with the host OS as the bounce buffer and copies the outgoing packets to it. Afterwards, the backend driver can copy the packets to the hypervisor as normal. As a result, the bounce buffer leads to excessive memory copies for I/O virtualization.

#### 2.3 Transport Layer Security (TLS)

TLS is an end-to-end security protocol designed to protect data in transit by leveraging cryptography. It has been commonly used by modern applications to secure their I/O payload in transit [6, 17, 49, 55, 61]. CVM solutions have made it a mandatory requirement for their applications [22, 26, 54]. Moreover, today's OSes, such as Linux, provide in-kernel TLS support, enabling userspace applications to offload TLS to the kernel for enhanced performance and expanded features [19]. As shown in Figure 1, in-kernel TLS allows the payload from the page cache to be encrypted without going through the userspace.

The industry currently implements the TLS protocol based on encryption algorithms such as AES-GCM [18] to assure the confidentiality and integrity of data simultaneously. The output of these encryption algorithms consists of encrypted ciphertext for confidentiality, and an authentication tag generated from the ciphertext for integrity. To provide complete data security protection, the correctness of both the ciphertext and its authentication tag must be guaranteed during encryption, and vice versa.

#### 2.4 Exitless Interrupt Virtualization

In the paravirtual I/O networking scenario, when a virtual NIC (i.e., network backend) receives some network packets, it notifies the guest VM with a virtual interrupt. The guest VM then needs to interact with the virtual interrupt controller to perform Acknowledgment (ACK) and End of Interrupt (EOI). Traditional techniques rely on the hypervisor to emulate interrupt delivery and interrupt controller access of guest VMs using trap-and-emulate approaches. However, virtualizing interrupts in this way can be a significant source of overhead, as each virtual interrupt's completion necessitates multiple VM exits and entries. To address this issue, modern hardware platforms have introduced the posted interrupt technique to enable exitless virtual interrupt delivery. They have also extended their interrupt controllers with specialized virtualization support to eliminate VM exits caused by ACK and EOI. Interrupt controllers with virtualization extensions are currently in production by all mainstream hardware vendors such as Intel, AMD, and ARM. Full-featured posted interrupt is available on the Intel platform, and it will soon be supported on other platforms (e.g., next-generation products with AMD AVIC [4] and ARM GICv4 [7]).

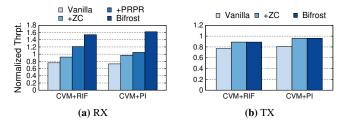

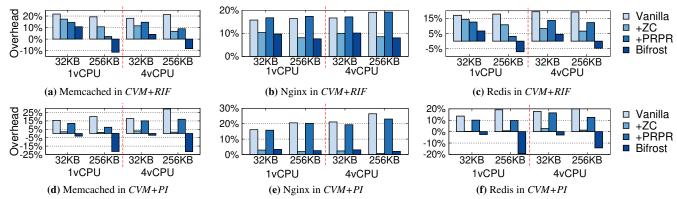

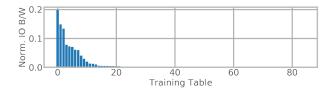

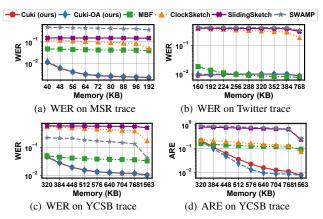

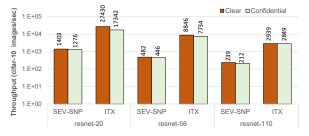

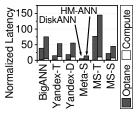

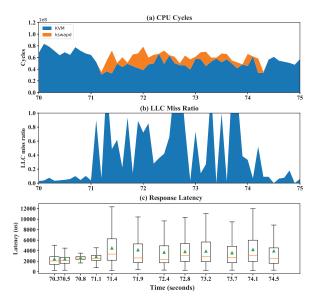

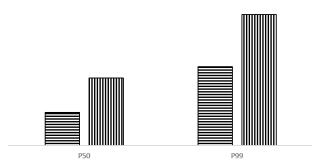

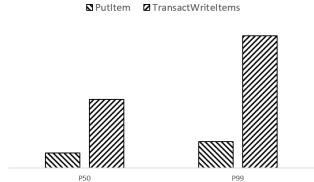

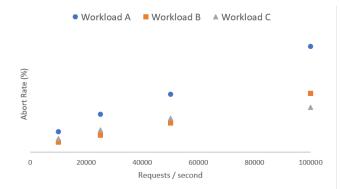

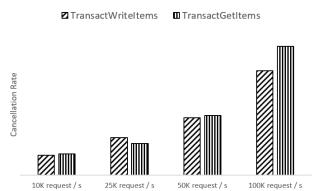

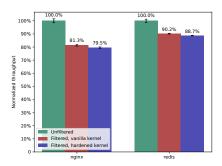

Figure 2: Normalized overhead compared with traditional VM in I/O-intensive applications. The Y-axis is the normalized overhead compared to the baseline of each group. CVM+PI represents CVM + Posted Interrupt.

#### 3 Analysis of CVM-IO Tax

In this section, we quantify the performance impact of the CVM-IO tax by comparing the I/O performance of existing CVMs with that of traditional VMs. The CPU execution time of I/O-intensive applications running in a CVM can be divided into two parts: 1) *Application workloads*: the time spent on executing application workloads, including business logic and payload processing. 2) The *CVM-IO tax*: the time spent on CVM-specific security protections and intrinsic network I/O procedures. It consists of VM exits, the bounce buffer mechanism, and the packet processing during the payload preparation for application workloads.