# conference

proceedings

# 17th USENIX Symposium on Operating Systems Design and Implementation (OSDI '23)

Boston, MA, USA July 10-12, 2023

Sponsored by

In cooperation with ACM SIGOPS

# **OSDI '23 Sponsors**

Platinum Sponsor amazon

# **Gold Sponsors**

**Silver Sponsors**

# **Bronze Sponsors**

## **Open Access Sponsor**

# **USENIX Supporters**

## **USENIX Patrons**

Amazon • Futurewei • Google • Meta

## **USENIX Benefactors**

Bloomberg • NetApp

## **USENIX Partners**

Thinkst Canary • Two Sigma

**Open Access Supporter**

Google

**Open Access Publishing Partner**PeerJ

### **USENIX** Association

# Proceedings of the 17th USENIX Symposium on Operating Systems Design and Implementation (OSDI '23)

#### © 2023 by The USENIX Association

#### All Rights Reserved

This volume is published as a collective work. Rights to individual papers remain with the author or the author's employer. Permission is granted for the noncommercial reproduction of the complete work for educational or research purposes. Permission is granted to print, primarily for one person's exclusive use, a single copy of these Proceedings. USENIX acknowledges all trademarks herein.

ISBN 978-1-939133-34-2

#### **Symposium Organizers**

**Program Co-Chairs**

Roxana Geambasu, Columbia University

Ed Nightingale, Apple

**Program Committee**

Atul Adya, Databricks

Rachit Agarwal, Cornell University

Nitin Agrawal, Google

Ramnatthan Alagappan, University of Illinois

at Urbana-Champaign Jeremy Andrus, Apple

Sebastian Angel, University of Pennsylvania

Mahesh Balakrishnan, Confluent

Adam Belay, MIT CSAIL

Emery Berger, University of Massachusetts Amherst

Edouard Bugnion, EPFL George Candea, EPFL

Kang Chen, Tsinghua University

Vijay Chidambaram, The University of Texas at Austin and

VMware Research

Mosharaf Chowdhury, University of Michigan

Byung-Gon Chun, Seoul National University and FriendliAI

Asaf Cidon, Columbia University Manuel Costa, Microsoft Research Landon Cox, Microsoft Research

Natacha Crooks, University of California, Berkeley

Jon Crowcroft, University of Cambridge Heming Cui, University of Hong Kong Dilma Da Silva, Texas A&M University Murat Demirbas, Amazon Web Services

Ittay Eyal, Technion—Israel Institute of Technology

Jason Flinn, Meta Bryan Ford, EPFL

Aishwarya Ganesan, University of Illinois at Urbana-Champaign and VMware Research

Phillip Gibbons, Carnegie Mellon University Yossi Gilad, Hebrew University of Jerusalem Joseph Gonzalez, University of California, Berkeley Andreas Haeberlen, University of Pennsylvania and Roblox

Steven Hand, Google Tim Harris, Microsoft Wenjun Hu, Yale University

Ryan Huang, Johns Hopkins University

Rüdiger Kapitza, Friedrich-Alexander-Universität

Erlangen-Nürnberg

Brad Karp, University College London Baris Kasikci, University of Michigan Eddie Kohler, Harvard University

Mathias Lécuyer, University of British Columbia Philip Levis, Google and Stanford University

Amit Levy, Princeton University Jinyang Li, New York University Hyeontaek Lim, Google

Wyatt Lloyd, Princeton University Jay Lorch, Microsoft Research Shan Lu, University of Chicago

Martin Maas, Google

Jonathan Mace, Max Planck Institute for Software Systems (MPI-SWS)

Ratul Mahajan, University of Washington and Intentionet

Z. Morley Mao, University of Michigan and Google

James Mickens, Harvard University

Thomas Moscibroda, Microsoft

Deepak Narayanan, Microsoft Research

Ravi Netravali, Princeton University Jason Nieh, Columbia University

Cristina Nita-Rotaru, Northeastern University

Shadi Noghabi, Microsoft Research Aurojit Panda, New York University

KyoungSoo Park, Korea Advanced Institute of Science and

Technology (KAIST)

Bryan Parno, Carnegie Mellon University

Daniel Peek, Meta

Peter Pietzuch, Imperial College London

Dan Ports, Microsoft Research

Costin Raiciu, University Politehnica of Bucharest

David Richardson, Apple

Luis Rodrigues, INESC-ID and Instituto Superior Técnico,

University of Lisbon

Christopher Rossbach, The University of Texas at Austin and

Katana Graph

Malte Schwarzkopf, Brown University

Marco Serafini, University of Massachusetts Amherst Marc Shapiro, Sorbonne-Université-LIP6 and Inria

Ji-Yong Shin, Northeastern University

Mark Silberstein, Technion—Israel Institute of Technology

Alex C. Snoeren, University of California, San Diego, and Google

Ion Stoica, University of California, Berkeley

Ryan Stutsman, University of Utah

Steven Swanson, University of California, San Diego

Adriana Szekeres, VMware Research Kaushik Veeraraghavan, Facebook

Geoffrey M. Voelker, University of California, San Diego

Roger Wattenhofer, ETH Zurich Michael Wei, VMware Research

Yubin Xia, Shanghai Jiao Tong University

Tianyin Xu, University of Illinois at Urbana-Champaign

Junfeng Yang, Columbia University

Ding Yuan, University of Toronto and YScope

Lidong Zhou, Microsoft Research

#### **Poster Session Co-Chairs**

Ryan Huang, University of Michigan Adriana Szekeres, VMware Research

**Steering Committee**

Marcos K. Aguilera, VMware Research

Andrea Arpaci-Dusseau, University of Wisconsin-Madison

Angela Demke Brown, University of Toronto

Jason Flinn, Meta

Casey Henderson, USENIX Association

Jon Howell, VMware Research Kimberly Keeton, Google

Hank Levy, University of Washington Jay Lorch, Microsoft Research

Shan Lu, University of Chicago James Mickens, Harvard University Timothy Roscoe, ETH Zurich

Margo Seltzer, University of British Columbia Geoff Voelker, University of California, San Diego

Hakim Weatherspoon, Cornell University and Exotanium, Inc.

**External Reviewers**

Hans-J. Boehm Michael Hicks Jon Howell Rohan Padhye David Mazières

# Message from the OSDI '23 Program Co-Chairs

Dear Colleagues,

Welcome to the 17th USENIX Symposium on Operating Systems Design and Implementation (OSDI '23).

Once again, we are co-locating OSDI and the USENIX Annual technical Conference (USENIX ATC '23). We are excited to be back in person in these two forums for such a large gathering of technical experts across academia and industry. We hope you come away from OSDI and USENIX ATC inspired, refreshed and re-engaged with the wider systems research community!

This year, OSDI received 255 submissions. We accepted 50 submissions, which is a 19.6% acceptance rate. This is inline with the 253 submissions and 19.4% acceptance rate from last year. In addition to the 50 papers accepted this year, 5 additional papers were accepted from the OSDI '22 Revise and Resubmit process. This brings the total program to 55 papers presented at OSDI across an incredibly wide breadth of areas of focus. Although this is 6 more papers than last year, we continue to be committed to a single-track conference at OSDI and have put together a 3-day program for all 55 papers.

Given the large number of submissions, we formed a program committee of 86 members in addition to the two program cochairs. There were also 5 external reviews where a particular area of expertise or evaluation was needed on a single paper. We are very grateful to the program committee for their diligence, focus, and optimism during the review process. OSDI is known for high quality reviews that help and inform the authors to produce their very best work.

The program committee reviewed submissions in two rounds. Every paper received at least three reviews in the first round. Roughly 40% of the papers were rejected during the first round of reviews. One paper was accepted after the first round of reviews concluded, and the remainder advanced to the second round. Papers then received 2 or 3 additional reviews. Subsequently, the PC had an asynchronous online discussion phase where an additional 35 papers were accepted and 77 papers were rejected. Thirty six papers were advanced to a synchronous, online two-day PC meeting. We purposefully organized the PC meeting by topic area, which allowed experts who might not have a paper in a particular area up for discussion, to dial in and participate in the areas most relevant to them. We finished the PC meeting on time, and had a great discussion from PC members all over the world. Each accepted paper was assigned a shepherd to work with the authors to revise the paper in response to reviewer feedback. The committee completed more than 1,000 reviews and posted hundreds of comments as part of the online discussion process. Finally, we did allow one of the program co-chairs to submit a paper. However, the paper was assigned a "paper administrator," and neither co-chair had any involvement in the review of that paper, and both were informed of the paper's outcome after the PC meeting concluded.

The program committee also chose to continue the revise-and-resubmit process. A small set of papers were recommended by the program committee to undergo this process. Those authors will have a much longer period of time (until August) to revise their papers, add important missing details, and/or run additional experiments, as requested by the PC. The original reviewers will review the revised submission. If accepted, the authors will be allowed to submit a "camera-ready" version of the paper in October of 2023 and then the authors will present the paper and have that paper officially included in the OSDI 2024 program. This early camera ready deadline allows authors to discuss the work (and have others cite it) well before the OSDI 2024 program appears.

Once the program was completed and the camera-ready deadline had passed, we began the process of selecting the Jay Lepreau Best Paper Award. We began by asking PC members for nominations and looking at the top-rated papers during the review process. We formed a small group of non-conflicted PC members who read each paper and agreed on the best paper of those chosen for consideration.

OSDI '23 had an artifact-evaluation committee that organized and evaluated the artifacts submitted by authors. The committee co-chairs this year are Jianyu Jiang, Nathan Rutherford, and Cesar A. Stuardo. Thirty-two papers submitted artifacts supporting their research. Twenty-nine papers received the Available badge. Thirty-one papers received the Functional badge, and 27 papers received the Reproduced badge, meaning the results in the paper were independently reproduced by the committee.

OSDI '23 had a poster submission process organized by co-chairs Adriana Szekeres and Ryan Huang. Thirty-three posters were accepted for display at the OSDI poster session.

Finally, as PC chairs, we rely on so many dedicated volunteers and professional staff to make this conference a reality. We thank the authors who submitted such high-quality work. This conference is first and foremost a forum for disseminating, sharing, discussing, and debating world-class systems research. Thank you for your hard work and innovation! We thank the PC members and external reviewers for their significant investment of time, energy, and insight into shaping the program. We thank Pierre Tholoniat and Roy Rinberg, who facilitated the PC meeting and made sure we ran the technology and not the other way around. We especially thank the USENIX staff, who have made chairing a conference like this one a well-oiled machine! Finally, we thank you for coming to this conference to engage with each other and with the authors of the accepted papers. This community is one we cherish, and one we are honored to have curated this year through our stewardship as cochairs.

We hope that you leave this conference energized and inspired.

Onwards!

Roxana Geambasu, *Columbia University* Ed Nightingale, *Apple* OSDI '23 Program Co-Chairs

## 17th USENIX Symposium on Operating Systems Design and Implementation (OSDI '23)

# July 10–12, 2023 Boston, MA, USA

# Monday, July 10

| Make Your Bits Go Faster                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ship your Critical Section, Not Your Data: Enabling Transparent Delegation with TCLocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RON: One-Way Circular Shortest Routing to Achieve Efficient and Bounded-waiting Spinlocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Userspace Bypass: Accelerating Syscall-intensive Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Triangulating Python Performance Issues with Scalene                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Relational Debugging — Pinpointing Root Causes of Performance Problems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Secure Your Bits I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Accountable authentication with privacy protection: The Larch system for universal login 8 Emma Dauterman, <i>UC Berkeley;</i> Danny Lin, <i>Woodinville High School;</i> Henry Corrigan-Gibbs, <i>MIT;</i> David Mazières, <i>Stanford University</i>                                                                                                                                                                                                                                                                                                                                                                          |

| K9db: Privacy-Compliant Storage For Web Applications By Construction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Encrypted Databases Made Secure Yet Maintainable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| LVMT: An Efficient Authenticated Storage for Blockchain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

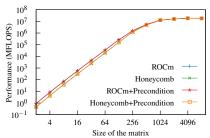

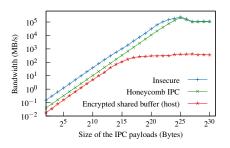

| Honeycomb: Secure and Efficient GPU Executions via Static Validation. 15.  Haohui Mai, PrivacyCore Inc.; Jiacheng Zhao, SKLP, Institute of Computing Technology, CAS; Zhongguancun Laboratory; and UCAS; Hongren Zheng, IIIS, Tsinghua University; Yiyang Zhao, SKLP, Institute of Computing Technology, CAS; and UCAS; Zibin Liu, BUPT; Mingyu Gao, IIIS, Tsinghua University; Cong Wang, IDEA Shenzhen; Huimin Cui, SKLP, Institute of Computing Technology, CAS; and UCAS; Xiaobing Feng, SKLP, Institute of Computing Technology, CAS; Zhongguancun Laboratory; and UCAS; Christos Kozyrakis, PrivacyCore Inc. and Stanford |

| Secure Your Bits II                                                                                               |

|-------------------------------------------------------------------------------------------------------------------|

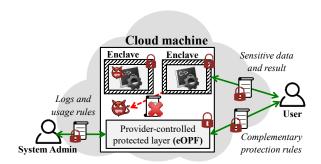

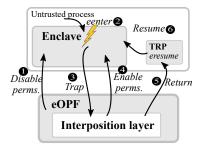

| An Extensible Orchestration and Protection Framework for Confidential Cloud Computing                             |

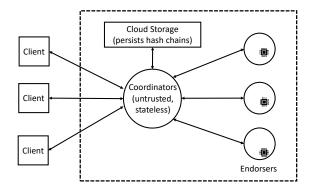

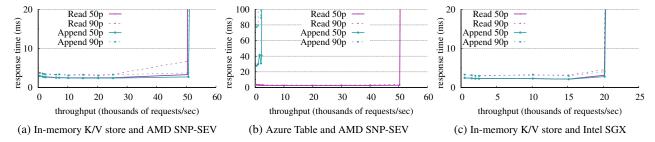

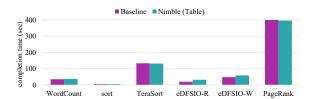

| Nimble: Rollback Protection for Confidential Cloud Services                                                       |

| Kerveros: Efficient and Scalable Cloud Admission Control                                                          |

| Security and Performance in the Delegated User-level Virtualization                                               |

| Core slicing: closing the gap between leaky confidential VMs and bare-metal cloud                                 |

| Tuesday, July 11                                                                                                  |

| Expanding, Hardening, and Deploying Your Bits                                                                     |

| ExoFlow: A Universal Workflow System for Exactly-Once DAGs                                                        |

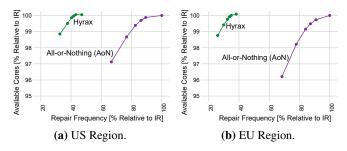

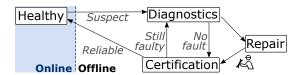

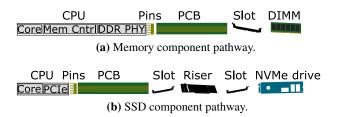

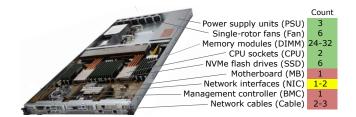

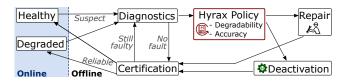

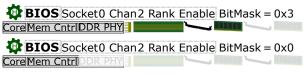

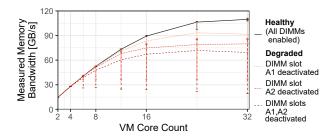

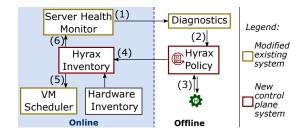

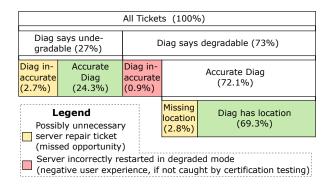

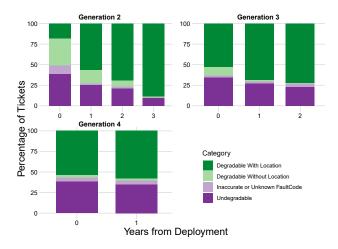

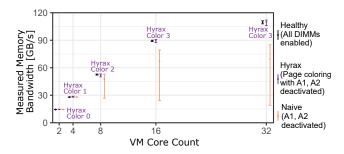

| Hyrax: Fail-in-Place Server Operation in Cloud Platforms                                                          |

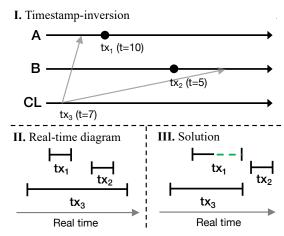

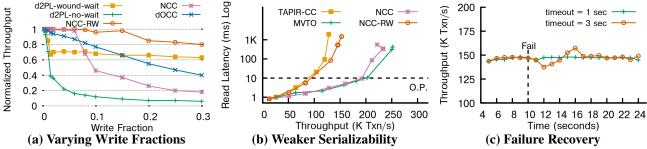

| NCC: Natural Concurrency Control for Strictly Serializable Datastores by Avoiding the Timestamp-Inversion Pitfall |

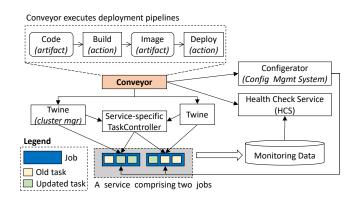

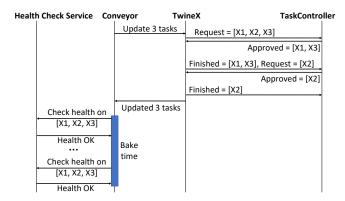

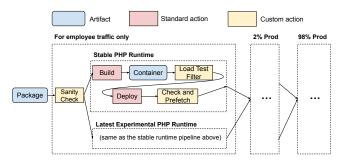

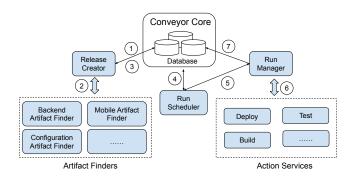

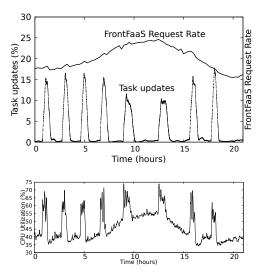

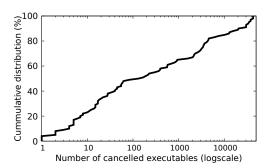

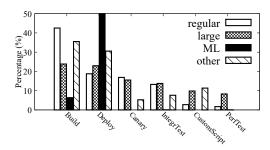

| Conveyor: One-Tool-Fits-All Continuous Software Deployment at Meta                                                |

| Query Your Bits                                                                                                   |

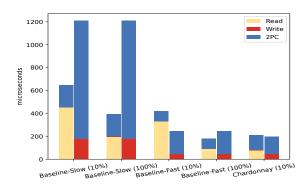

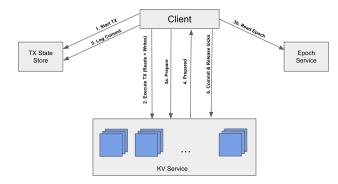

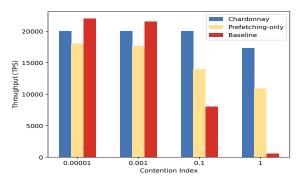

| Chardonnay: Fast and General Datacenter Transactions for On-Disk Databases                                        |

| ScaleDB: A Scalable, Asynchronous In-Memory Database                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 361         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| VBASE: Unifying Online Vector Similarity Search and Relational Queries via Relaxed Monotonicity                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |

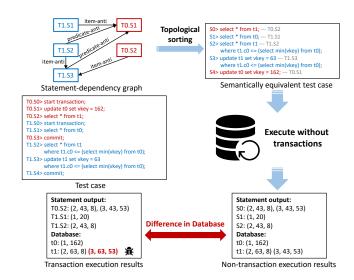

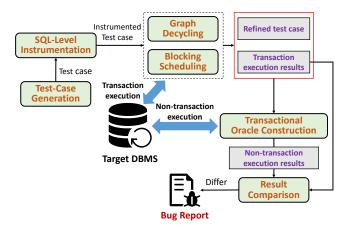

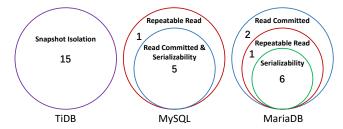

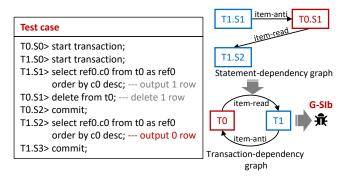

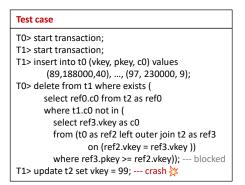

| <b>Detecting Transactional Bugs in Database Engines via Graph-Based Oracle Construction</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 397         |

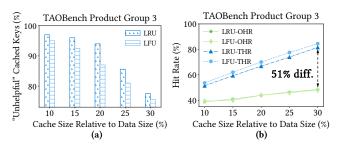

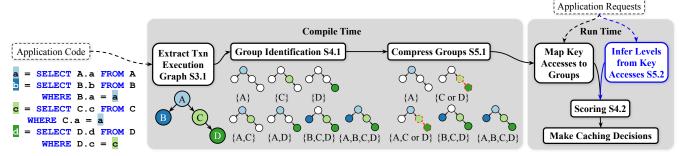

| Take Out the TraChe: Maximizing (Tra)nsactional Ca(che) Hit Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |

| Store Your Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |

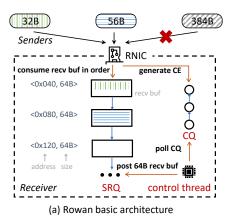

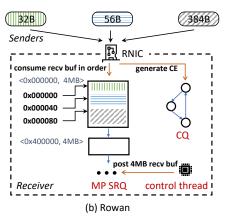

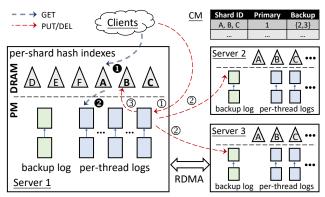

| Replicating Persistent Memory Key-Value Stores with Efficient RDMA Abstraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 441         |

| eZNS: An Elastic Zoned Namespace for Commodity ZNS SSDs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 461         |

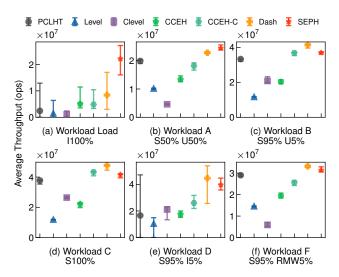

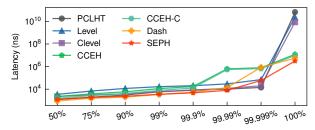

| SEPH: Scalable, Efficient, and Predictable Hashing on Persistent Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>47</b> 9 |

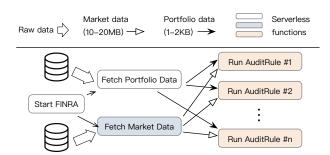

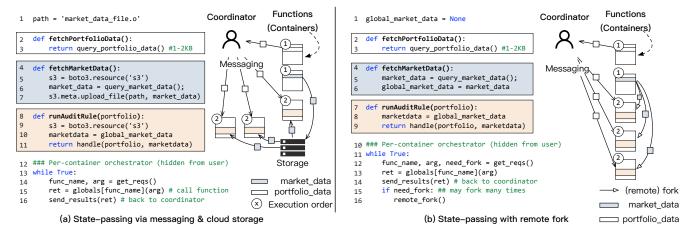

| No Provisioned Concurrency: Fast RDMA-codesigned Remote Fork for Serverless Computing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 497         |

| Manage Your Bits I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |

| Johnny Cache: the End of DRAM Cache Conflicts (in Tiered Main Memory Systems)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 519         |

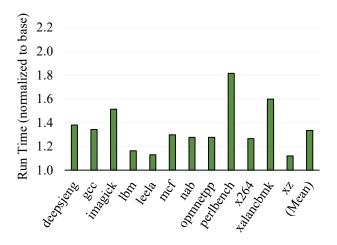

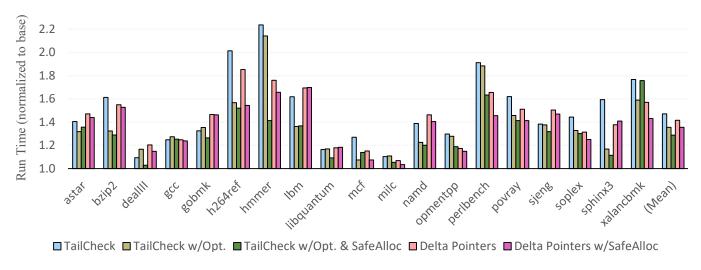

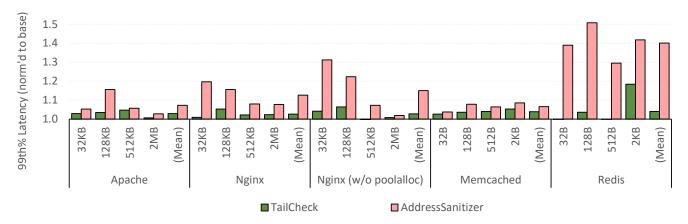

| TAILCHECK: A Lightweight Heap Overflow Detection Mechanism with Page Protection and Tagged Pointers 5  Amogha Udupa Shankaranarayana Gopal, Raveendra Soori, Michael Ferdman, and Dongyoon Lee, Stony Brook University                                                                                                                                                                                                                                                                                                                                                   | 535         |

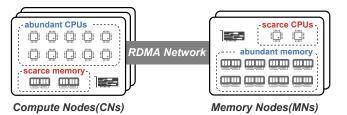

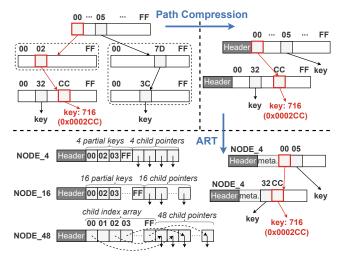

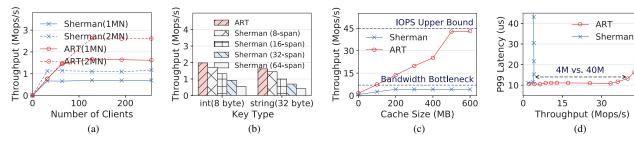

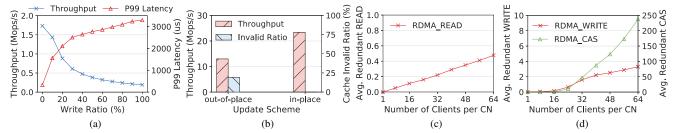

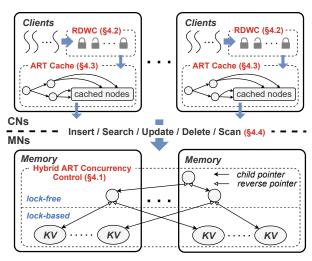

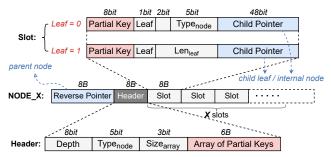

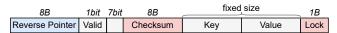

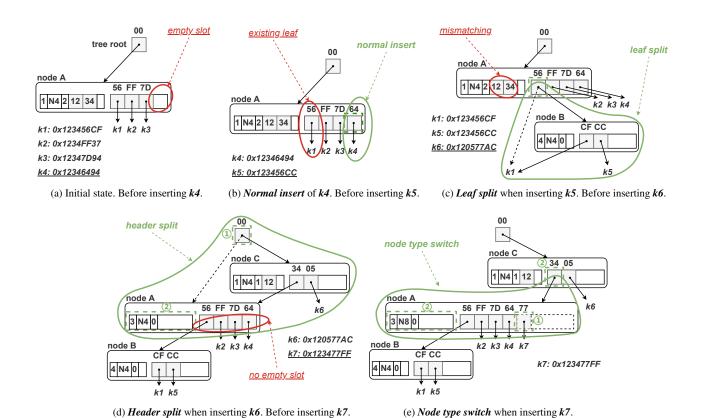

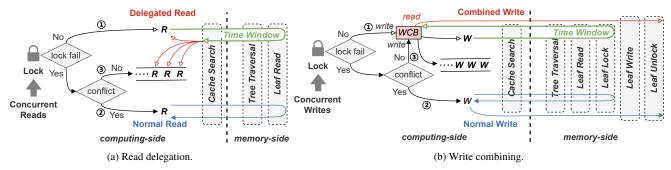

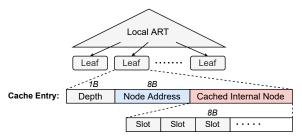

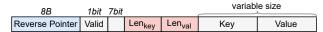

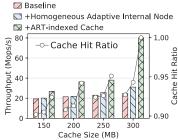

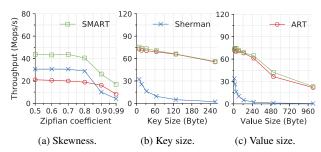

| SMART: A High-Performance Adaptive Radix Tree for Disaggregated Memory  Xuchuan Luo, School of Computer Science, Fudan University; Pengfei Zuo, Huawei Cloud; Jiacheng Shen and Jiazhen Gu, The Chinese University of Hong Kong; Xin Wang, School of Computer Science, Fudan University; Shanghai Key Laboratory of Intelligent Information Processing, Shanghai, China; Michael R. Lyu, The Chinese University of Hong Kong; Yangfan Zhou, School of Computer Science, Fudan University; Shanghai Key Laboratory of Intelligent Information Processing, Shanghai, China | 553         |

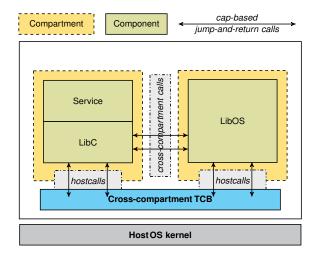

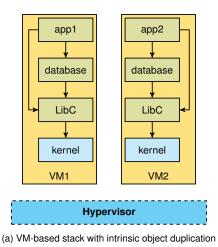

| ORC: Increasing Cloud Memory Density via Object Reuse with Capabilities  Vasily A. Sartakov, Lluís Vilanova, and Munir Geden, Imperial College London; David Eyers, University of Otago; Takahiro Shinagawa, The University of Tokyo; Peter Pietzuch, Imperial College London                                                                                                                                                                                                                                                                                            | 573         |

| Manage Your Bits II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             |

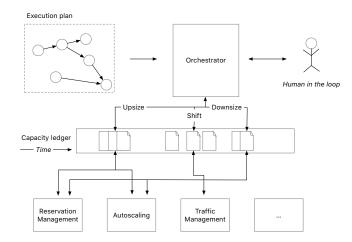

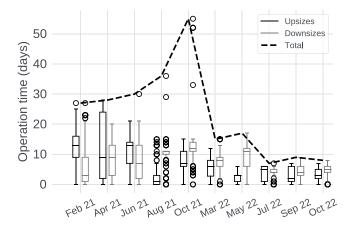

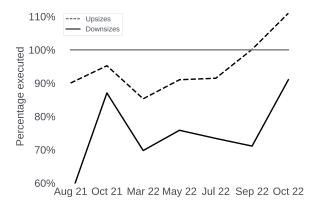

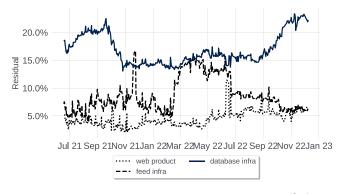

| Global Capacity Management With Flux                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 589         |

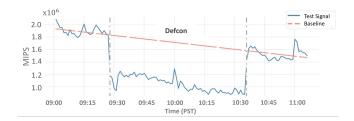

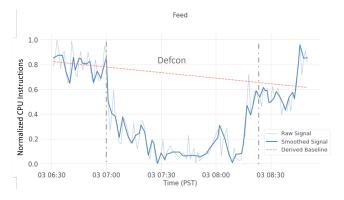

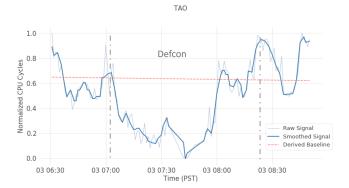

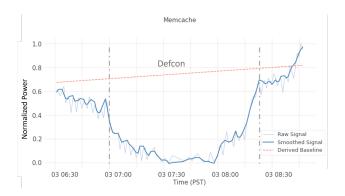

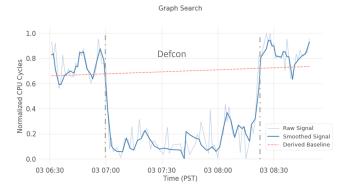

| Defcon: Preventing Overload with Graceful Feature Degradation                                     | 07  |

|---------------------------------------------------------------------------------------------------|-----|

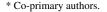

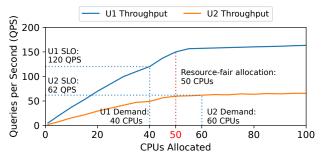

| <b>Cilantro: Performance-Aware Resource Allocation for General Objectives via Online Feedback</b> | 23  |

| Karma: Resource Allocation for Dynamic Demands                                                    | 45  |

| Wednesday, July 12                                                                                |     |

| Train Your Bits I                                                                                 |     |

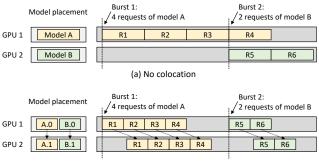

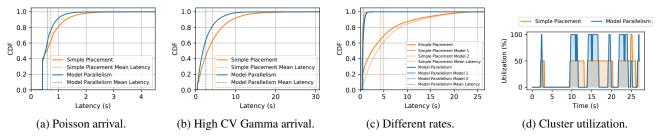

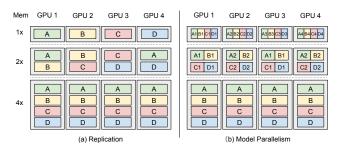

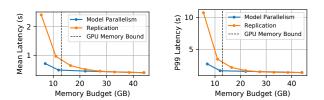

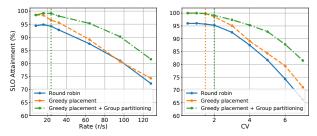

| AlpaServe: Statistical Multiplexing with Model Parallelism for Deep Learning Serving              | 63  |

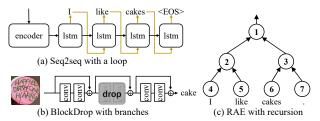

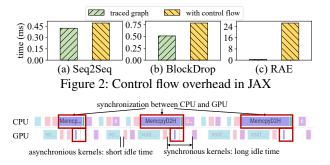

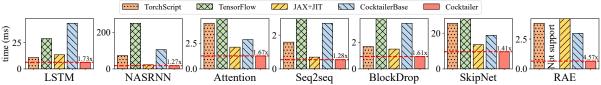

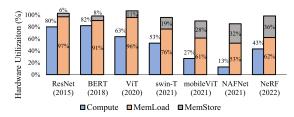

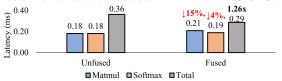

| Cocktailer: Analyzing and Optimizing Dynamic Control Flow in Deep Learning                        | 81  |

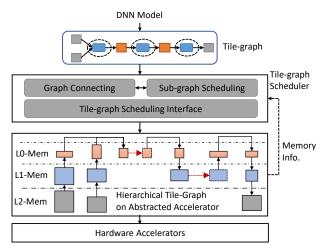

| Welder: Scheduling Deep Learning Memory Access via Tile-graph                                     |     |

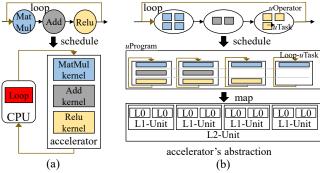

| Effectively Scheduling Computational Graphs of Deep Neural Networks toward Their Domain-Specific  |     |

| Accelerators                                                                                      | '19 |

| Train Your Bits II                                                                                |     |

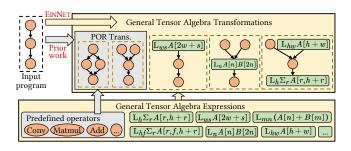

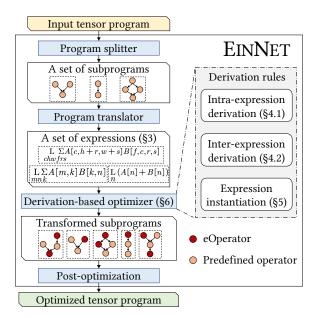

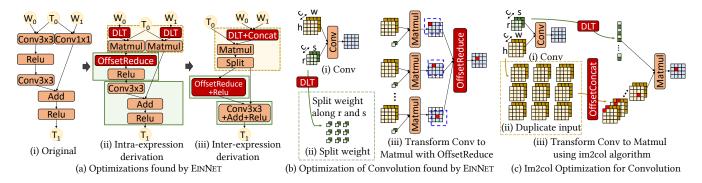

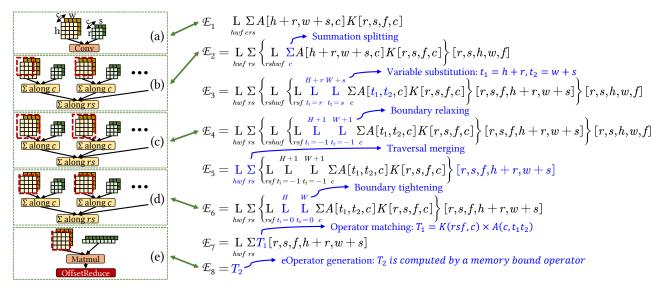

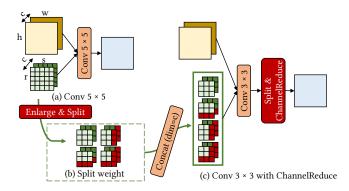

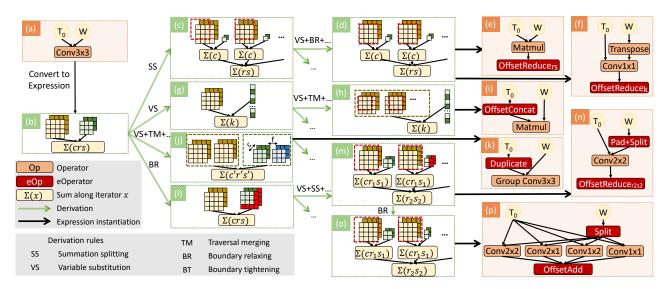

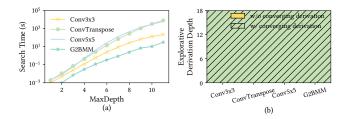

| EINNET: Optimizing Tensor Programs with Derivation-Based Transformations                          |     |

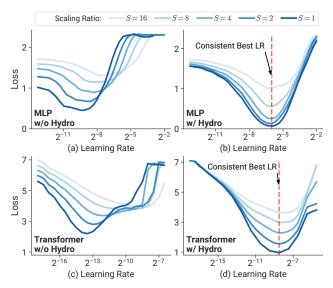

| Hydro: Surrogate-Based Hyperparameter Tuning Service in Datacenters                               | 57  |

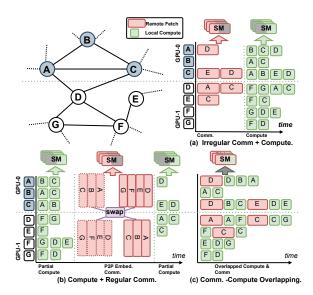

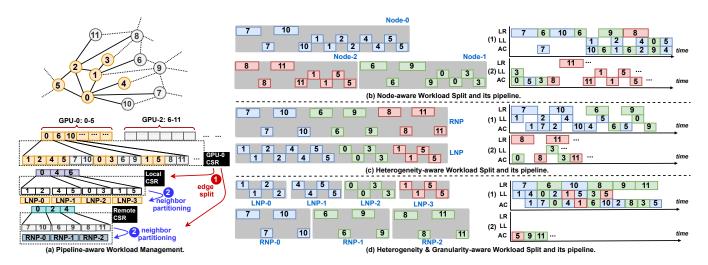

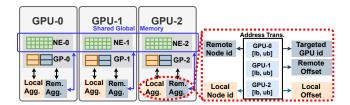

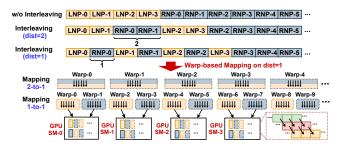

| MGG: Accelerating Graph Neural Networks with Fine-Grained Intra-Kernel Communication-Computation  |     |

| Pipelining on Multi-GPU Platforms                                                                 | 79  |

| Optimizing Dynamic Neural Networks with Brainstorm                                                | 97  |

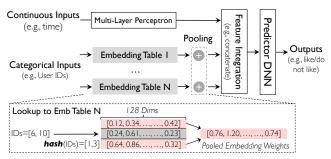

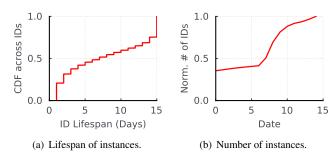

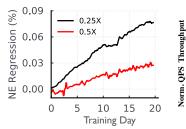

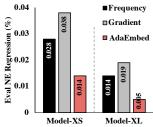

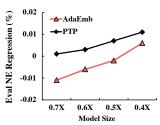

| AdaEmbed: Adaptive Embedding for Large-Scale Recommendation Models                              |  |  |  |

|-------------------------------------------------------------------------------------------------|--|--|--|

| Verify Your Bits                                                                                |  |  |  |

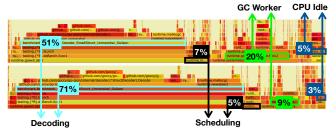

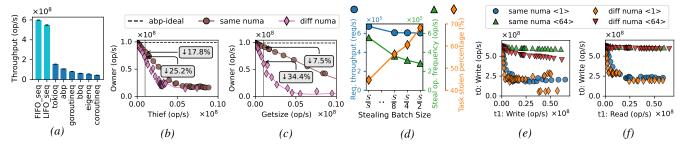

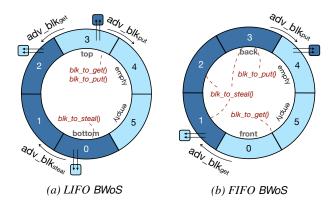

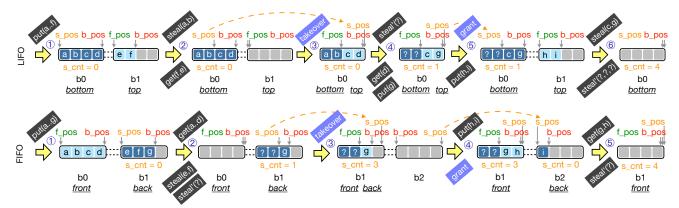

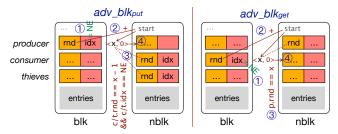

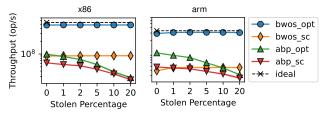

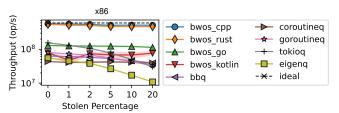

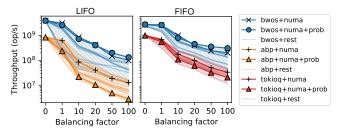

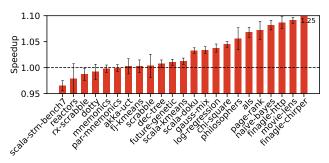

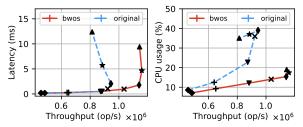

| BWoS: Formally Verified Block-based Work Stealing for Parallel Processing                       |  |  |  |

| Spoq: Scaling Machine-Checkable Systems Verification in Coq                                     |  |  |  |

| Verifying vMVCC, a high-performance transaction library using multi-version concurrency control |  |  |  |

| Automated Verification of Idempotence for Stateful Serverless Applications                      |  |  |  |

| Sharding the State Machine: Automated Modular Reasoning for Complex Concurrent Systems          |  |  |  |

| Transfer Your Bits                                                                              |  |  |  |

| Flor: An Open High Performance RDMA Framework Over Heterogeneous RNICs                          |  |  |  |

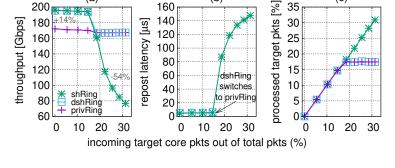

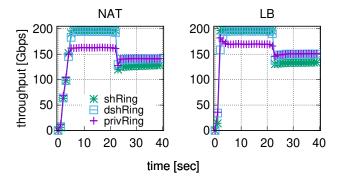

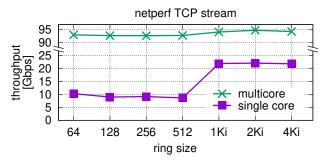

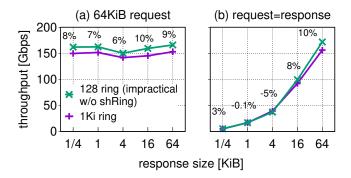

| ShRing: Networking with Shared Receive Rings                                                    |  |  |  |

| ServiceRouter: Hyperscale and Minimal Cost Service Mesh at Meta                                 |  |  |  |

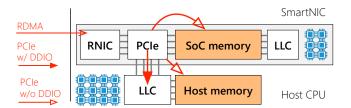

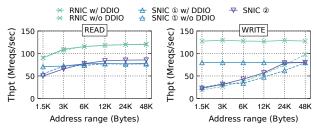

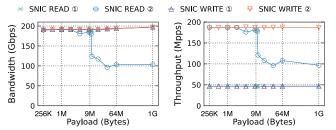

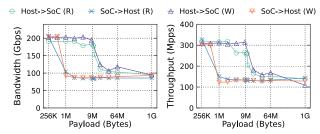

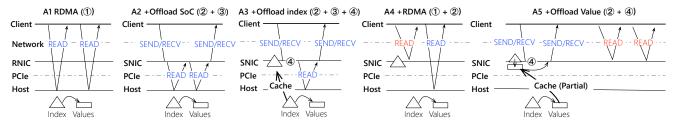

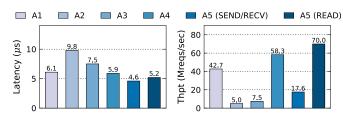

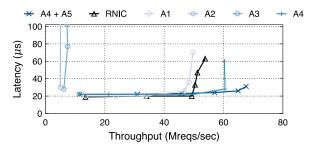

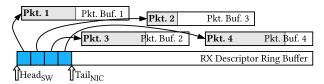

| Characterizing Off-path SmartNIC for Accelerating Distributed Systems                           |  |  |  |

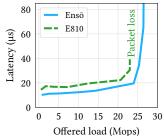

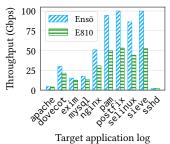

| Ensō: A Streaming Interface for NIC-Application Communication                                   |  |  |  |

## Ship your Critical Section, Not Your Data: Enabling Transparent Delegation with TCLocks

Vishal Gupta Kumar Kartikeya Dwivedi\* Yugesh Kothari Yueyang Pan

Diyu Zhou Sanidhya Kashyap

EPFL \*SRMIST

#### **Abstract**

Today's high-performance applications heavily rely on various synchronization mechanisms, such as locks. While locks ensure mutual exclusion of shared data, their design impacts application scalability. Locks, as used in practice, move the lock-guarded shared data to the core holding it, which leads to shared data transfer among cores. This design adds unavoidable critical path latency leading to performance scalability issues. Meanwhile, some locks avoid this shared data movement by localizing the access to shared data on one core, and shipping the critical section to that specific core. However, such locks require modifying applications to explicitly package the critical section, which makes it virtually infeasible for complicated applications with large code bases, such as the Linux kernel.

We propose *transparent delegation*, in which a waiter automatically encodes its critical section information on its stack and notifies the combiner (lock holder). The combiner executes the shipped critical section on the waiter's behalf using a lightweight context switch. Using transparent delegation, we design a family of locking protocols, called TCLocks, that requires zero modification to applications' logic. The evaluation shows that TCLocks provide up to 5.2× performance improvement compared with recent locking algorithms.

#### 1 Introduction

Synchronization mechanisms are the basic building blocks for today's high-performance concurrent applications. In fact, applications heavily rely on locks as a concurrency control mechanism, as they provide a set of simple programming APIs for users to mediate concurrent access to shared data. Besides ensuring program correctness, locks also affect the scalability of applications [33, 34, 49]. For instance, various high-performance applications, such as the Linux kernel, have moved from coarse-grained to finegrained locks [52] for minimizing the length of the critical section. However, thanks to diverse workloads and applications, the scalability problem due to lock algorithms still remains at large [41, 55, 62, 70].

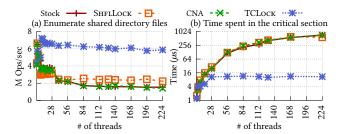

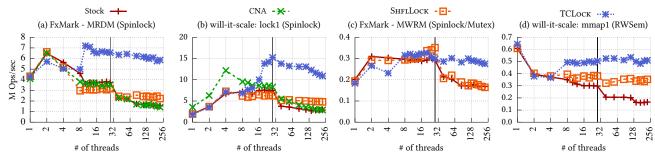

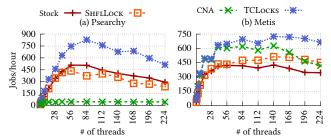

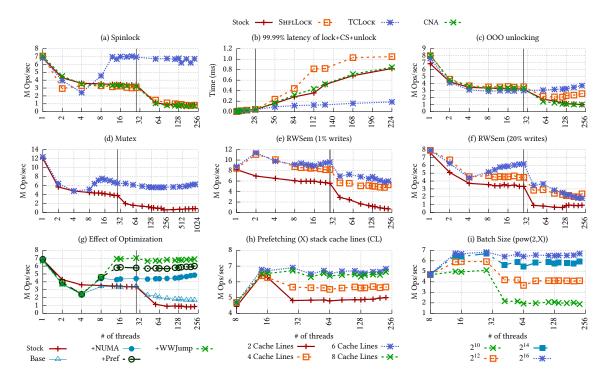

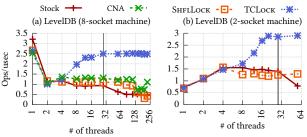

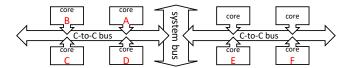

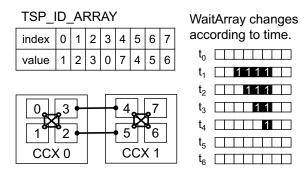

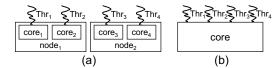

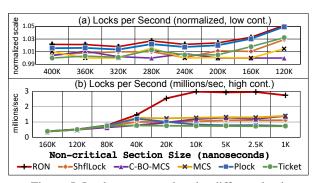

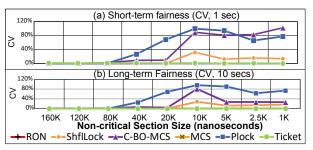

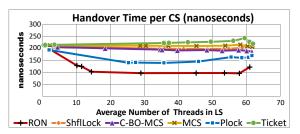

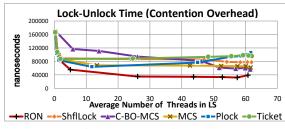

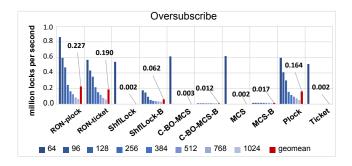

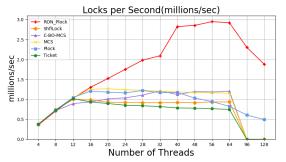

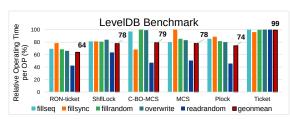

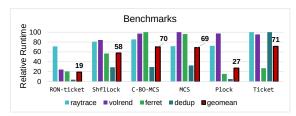

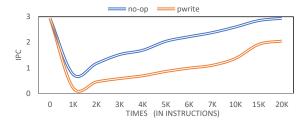

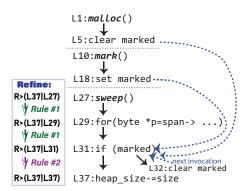

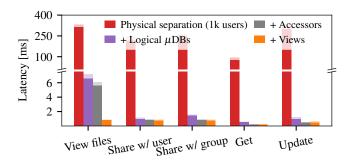

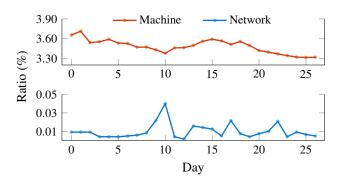

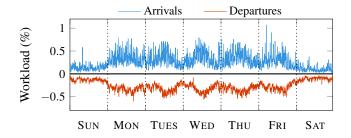

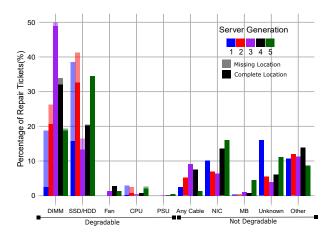

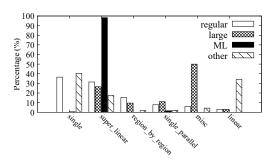

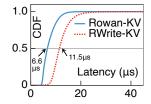

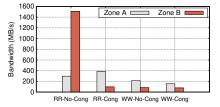

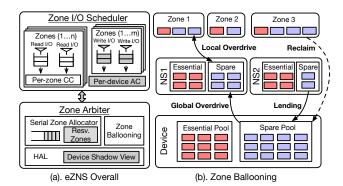

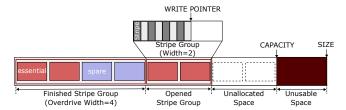

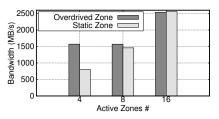

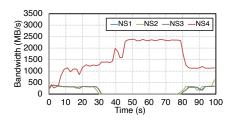

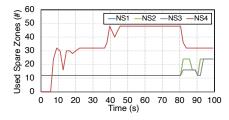

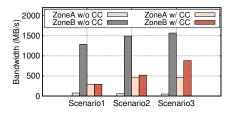

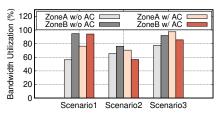

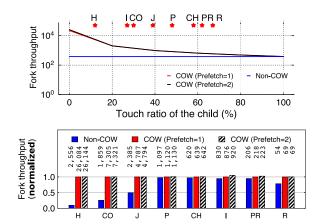

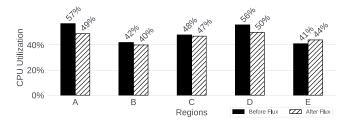

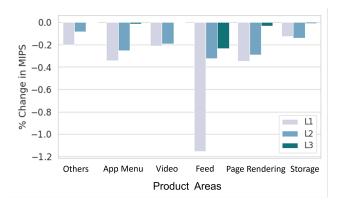

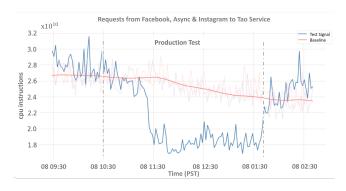

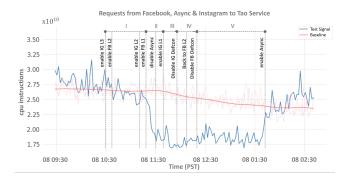

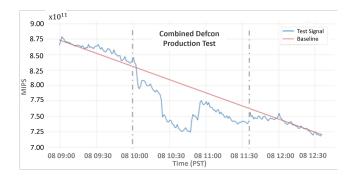

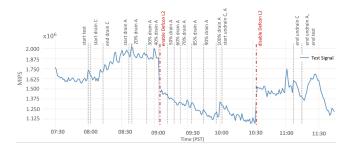

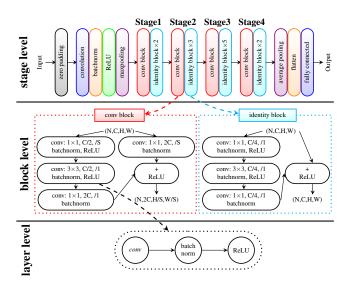

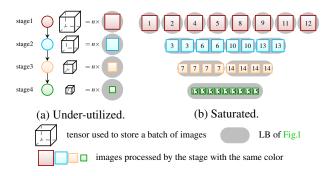

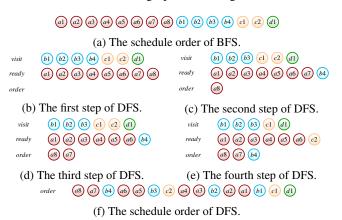

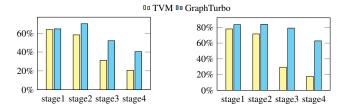

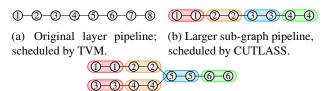

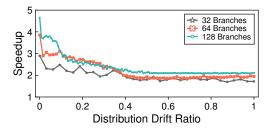

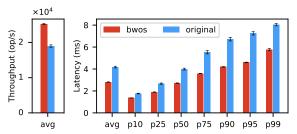

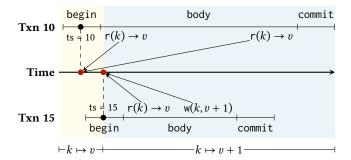

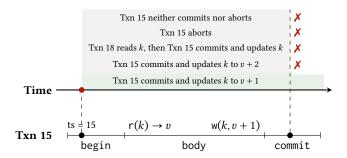

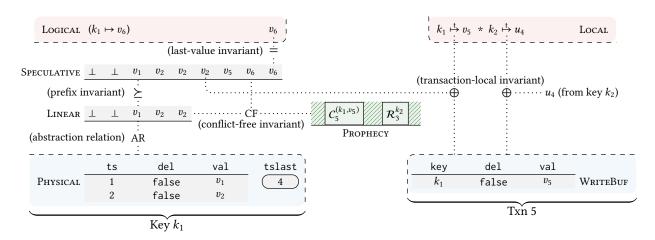

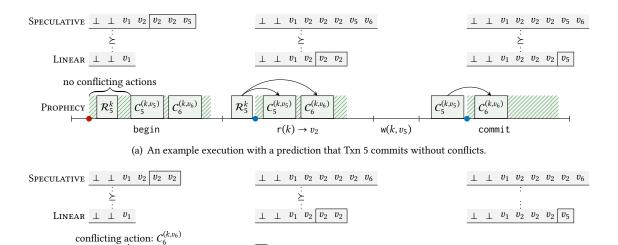

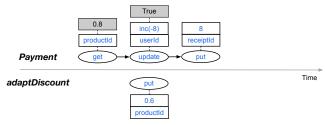

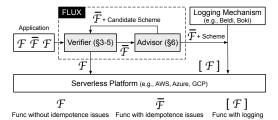

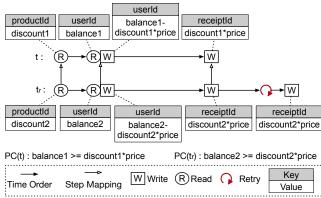

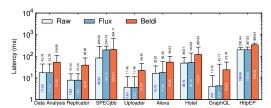

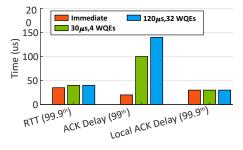

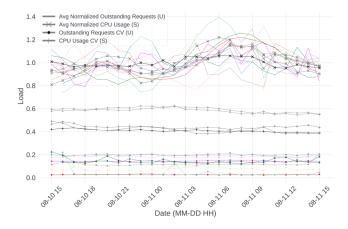

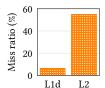

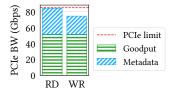

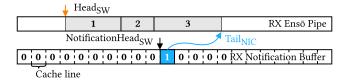

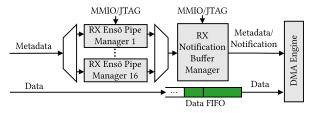

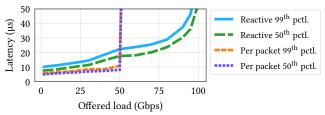

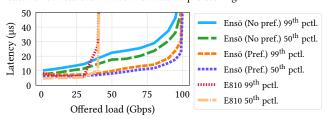

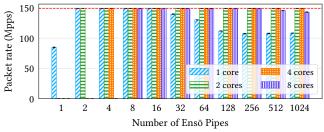

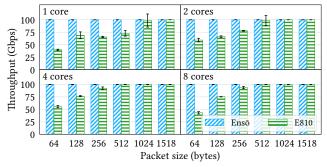

Figure 1: Impact of locks on a file-system micro-benchmark [62]. We compare three traditional lock algorithms: Linux's qspin-lock (*Stock*) [41], CNA [43] and Shfllock [52] with our proposed TCLock. (a) Enumerating files in a shared directory on an 8-socket 224-core machine. (b) Time spent in the critical section: moving the critical section context (TCLock) compared with moving critical section shared data (*Stock*, CNA, and Shfllock).

As a result, research in lock algorithms focuses on minimizing the contention on cache-lines containing the lock word and shared data. The most widely used algorithms always move the shared data to the core executing the critical section [30, 41, 43, 52, 53, 60]. Lock evolution within this design philosophy has focused on reducing contention on the lock word. However, such a lock design still moves shared data across cores for every lock acquisition. Figure 1 shows that such shared data access cost increases with increasing cores, thereby limiting the scalability of applications.

On the other end of the design spectrum, some algorithms adopt the request-response style of communication, also called delegation-style locking [37, 47, 51, 56, 64, 67]. Specifically, waiters delegate their critical section execution context to a dedicated core [56, 67] or a *combiner* [47, 51] that executes that function on behalf of each waiter in a specific order. Figure 1 illustrates that this design outperforms traditional locks and improves application performance. In particular, such a lock design minimizes the shared data movement, and ensures almost constant critical section latency regardless of the number of threads.

Despite potential performance gains, the practical design and implementation of delegation-style locks faces several challenges. First, applications require major rewriting to explicitly encapsulate and pass the critical section as a function pointer [51, 56, 67]. Unfortunately, this rewriting becomes impractical for applications with large code bases, such as the Linux kernel, which has over 180k lock API call sites [52]. Second, every delegation-based work focuses on situations involving a single lock contention. However, today's applications often employ fine-grained locking and may acquire multiple locks for operations, such as memory, scheduler, and storage management in the Linux kernel [4, 12, 13, 20]. Finally, the third challenge involves managing the per-CPU or per-thread variables, which applications heavily depend on for either performance or correctness.

In this paper, we take the first step towards making delegation-based locks practical for concurrent applications with large code bases. We introduce the idea of transparent delegation, which enables developers to utilize delegationstyle locking without rewriting the application. Our transparent delegation approach encapsulates the critical section using two observations: First, a thread's stack and CPU registers contain the state of the waiter's thread. Second, using the lock/unlock API pushes the thread's context on its stack. Thus, a waiter saves its critical section context using CPU registers and stack pointer, and calling the lock API as a function. Finally, the combiner executes the waiter's critical section on its behalf by assuming the role of the waiter using a lightweight context switch mechanism [29, 59]. This context-switch mechanism is transparent to the application.

Using transparent delegation, we design a new family of locks called TCLocks that augment existing locks, such as test-and-set (TAS) and MCS, by employing the combining technique for batching waiters' requests [47]. Our first lock is a spinlock, where waiters continuously spin while awaiting the lock. The combiner can execute multiple waiter's critical section before passing its role based on a counter-based mechanism. Similar to our prior work (SHFLLOCKS) [52], our algorithms can enforce hardware and software policies on the fly. In particular, our spinlock version also incorporates NUMA-awareness policy. We then integrate the core oversubscription policy [52] to design a blocking lock, where the waiter can sleep while waiting for the lock. Lastly, we design a phase-based readers-writer lock built on top of our blocking lock.

Applying TCLocks directly in highly concurrent systems presents its own set of challenges. First, transparent delegation violates the single-writer property of a thread's stack, meaning that two threads (the combiner and the waiter) writing to the same stack can cause data races and stack corruption. Waiters need access to a stack due to specific events, such as interrupts in the kernel space, signals in userspace, and scheduling of waiting threads. We address the data-race issue using a per-thread ephemeral stack that a waiter switches to between the acquire and release phases.

Second, most concurrent applications use multi-level locking [4, 20, 28] and out-of-order (OOO) unlocking [12, 13]

for higher concurrency and better scalability. TCLocks handle the arbitrary level of nested combining by maintaining combiner-specific state on the ephemeral stack before acquiring the nested lock. Meanwhile, we handle OOO unlocking by keeping track of the order of acquired locks. We delay the release of OOO unlocked locks until the order is the inverse of acquired locks. This effectively flattens the release of locks.

We evaluate TCLocks in both kernel space and userspace on NUMA machines. TCLocks improve the performance within and across sockets. Specifically, TCLocks boost application throughput by  $1.7-5.2 \times$  compared to the locks used in the Linux kernel and state-of-the-art locks, respectively.

In summary, this paper makes the following contributions:

- Design technique. We introduce a new design technique called transparent delegation. Locks with this technique allow developers to use the same APIs as traditional locks while benefiting from the scalability improvements provided by delegation-style locking.

- · Delegation-based lock family. We implement TCLocks that employ transparent delegation. We first design a spinning lock and extend it to blocking and readers-writer locks, utilizing per-thread ephemeral stacks to manage the parking of waiters.

- Practical application. TCLocks incorporate various lock use scenarios, including nested locking and outof-order unlocking. This approach allows us to realize the potential of delegation-style locking for the Linux kernel without modifying any code.

#### Background

While executing a critical section, a thread accesses three types of memory locations (data):

- 1. **Lock word**, *i.e.*, its structure that determines the exclusive access for a thread.

- 2. **Shared data** among threads guarded by a lock word, accessible only to the thread holding the lock.

- 3. **Thread-local data** like stack and per-thread variables. Most lock designs minimize the contention on the lock word, while some minimize the movement of shared data. Hence, there are two design philosophies based on shared data movement: traditional and delegation-style. We now discuss the evolution of locks based on these design philosophies. Later, we touch upon the systems-level challenges that are specific to delegation-style locks.

#### Traditional Locks

Traditional lock design adheres to the principle of moving data to computation. A core executes the critical section by moving shared data into its cache. Consequently, this design moves cache lines of both the lock word and shared data across cores while executing the critical section. The evolution of traditional lock algorithms [50] has focused on minimizing cache-line movement of the lock word. For example, queue-based locks [41, 42, 44, 58, 60, 68] minimize cache-line contention due to the lock word. Hierarchical locks [39, 46, 57, 66] further reduce the cache-line contention on non-uniform memory access (NUMA) machines, where accessing a local-socket memory location is faster than a remote one. These locks amortize the remote access cost of the lock word by reordering the wait queue to pass the lock within the same socket. ShflLock [52] and CNA [43] further generalize hierarchical lock design by reordering the wait queue based on various hardware and software policies. Moreover, our recent work [65] has also shown that the reordering policy can be changed dynamically without kernel compilation.

Readers-writer locks also follow traditional lock design, with most locks aiming to minimize contention on the lock word [36, 54, 61]. These locks augment mutually exclusive locks with different types of read indicators based on workload requirements. Some examples include centralized [61], per-socket [38], and per-CPU [40, 63, 71] indicators. These locks also require moving shared data across cores, even though they offer a broader semantics of mutual exclusion.

Traditional locks do not require modifying applications since the lock/unlock programming APIs remain consistent. However, these locks move shared data cache lines among cores while executing the critical section. Unfortunately, this lock design incurs shared data movement for every critical section execution, thereby increasing critical section execution latency. Moreover, this latency grows with increasing core count (Figure 1 (b)), which saturates the throughput without efficiently utilizing hardware.

#### 2.2 Delegation-style Locks

Delegation-style locks follow the principle of moving computation to data [45, 47, 51, 56, 64, 67]. These locks use an old technique called combining that has been used in hardware and software to mitigate memory contention by combining requests for the same memory location. In this approach, waiters pack their critical section as a function and pass that function pointer to the combiner as a request. The combiner then executes the waiter's function and notifies it upon completion. Executing the critical section on the same core eliminates shared data movement, leading to improved application throughput with increasing core count (Figure 1).

However, this lock design has a critical limitation. It does not provide the same lock/unlock APIs as traditional locks [47, 67]. Consequently, we need to modify applications, which involves identifying each critical section in the code, wrapping it as a function, and modularizing the application logic for delegation. Modifying application logic to encapsulate the critical section as a function is quite challenging and even impossible in some cases [46]. For instance, Roghanchi et al. [67] reported modifying  $\sim$ 1,500 lines of code (LoC) to enable delegation for Memcached. This limitation, unfortunately, prevents the scalability offered by delegation-style locking from being applied to existing real-world applications, such as Linux, which comprises 28M LoC with more than 180k static lock call sites.

#### The Incompatibility of Delegation in Concurrent **Applications**

Real-world applications, such as the Linux kernel, employ fine-grained locking in multiple execution contexts. Finegrained locking mostly involves acquiring multiple nested locks when working with several objects. To prevent deadlocks, the nested locks are acquired in a specific order, but they can be released in arbitrary order to enhance concurrency [12, 13]. However, none of the delegation approaches handle such common, but challenging cases. We measured that both nested locking calls and OOO unlocking calls are quite prevalent. For instance, booting Linux results in  $\sim$ 80k nested locking calls and  $\sim$ 20k OOO unlock calls. Thus, addressing these cases is essential to make delegation-style locks practical for every concurrent systems software.

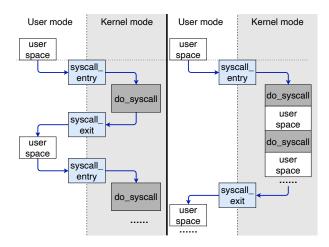

In addition, the Linux kernel can call locks from various contexts. These contexts comprise of task [25] and interrupts (e.g., non-maskable interrupt context [11], HardIRQ context [6, 7], or SoftIRQ context [23])). The kernel code typically executes in the task context. Depending on the kernel configuration, a scheduler can preempt or migrate a task to another CPU. Nevertheless, in special execution contexts, such as interrupts, or code regions that disable CPU preemption and migration, the scheduler prohibits the migration of such contexts. The Linux kernel code also heavily utilizes per-CPU variables and implicitly relies on stable access to these variables in such special execution contexts. Traditional lock design does not require any handling for special execution contexts because the critical section executes on the core that acquires the lock. In contrast, delegation-style locks break this property, necessitating special handling for these cases, i.e., special contexts and stable access to per-CPU variables.

Goal. In accordance with the general design principle of minimizing data movement [43, 52], our objective is to reduce data movement for both lock word and shared data. Unlike existing delegation-style locks, we avoid making any code modifications. Hence, we take the initial step towards achieving the goal of transparently enabling delegation-style locking for any real-world application, including the OS.

#### **TCLocks** 3

We propose transparent delegation, a practical lock-design technique for real-world applications that allow developers to use the same lock/unlock APIs as traditional locks without modifying the application code. Transparent delegation involves two steps: First, it automatically encapsulates a critical section of arbitrary length in a set of registers and the thread stack. Second, waiters pass this encapsulated information to the combiner for execution. As a result, our approach enables applications to enjoy scalability without any modification. We apply this technique to design a family

of lock algorithms called TCLOCKS, that transparently delegate waiters' requests to the combiner. TCLOCKS comprises spinning (§3.2) and blocking (§3.4) locks. We extend the blocking lock with read indicators to design a phase-based readers-writer blocking lock (§3.5) incorporating hardware and software-based optimizations (§3.6).

#### 3.1 TCLock Design

We first discuss a set of insights and techniques that allows us to design and implement TCLocks.

**Transparent delegation.** When executing a critical section, a thread can access both shared data (*e.g.*, global variables, heap) and thread-local data (*e.g.*, registers, stack, and per-thread variables). In delegation-style locking, although shared data is globally available to all threads, the combiner requires access to the waiter's thread-local data and the set of instructions for executing its critical section.

Our technique overcomes the challenge of thread-local data and critical section context using three key insights.

- 1. A thread's execution context is well-defined by hardware, with thread-specific CPU registers and the stack containing all information for executing the critical section [2, 8, 10].

- 2. A waiter busy-waits without modifying its state once it sends its request to the combiner. It exits only after receiving the response from the combiner.

- 3. Calling the lock API as a function<sup>1</sup> ensures that hardware pushes the next instruction onto the stack, making the critical section's start address available to the combiner for executing the critical section.

Using these insights, the combiner pops the start address of a critical section from the waiter's stack using a *return* instruction and executes it. After completing the critical section, calling the unlock API pushes the first instruction of the non-critical section onto the waiter's stack. The waiter resumes executing the non-critical section after receiving a notification from the combiner. Thus, transparent delegation allows waiters to seamlessly pass context and resume after the critical section's execution.

Avoiding concurrent stack access with an ephemeral stack. To ensure program correctness, transparent delegation must prevent concurrent accesses to a thread's execution stack. Ideally, a waiter busy-waits for notification during its critical section execution. However, certain events, such as interrupts in kernel space, signals in user space, and the waiter's parking and wake-up mechanism [32] can access the waiter's stack during the execution of its delegated critical section. As a result, naive transparent delegation via stack switching violates the fundamental single-writer stack principle, leading to potential stack state corruption.

To address this issue, we introduce an initially empty, separate stack called the *ephemeral stack*. Each waiter switches to its ephemeral stack during lock acquisition, and delegates

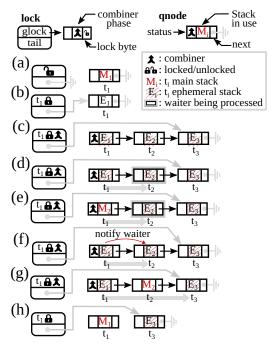

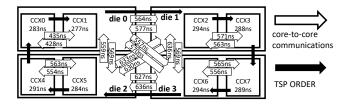

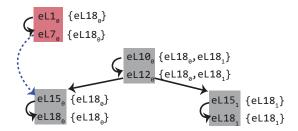

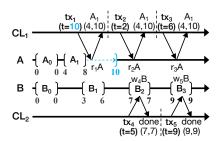

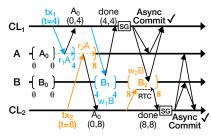

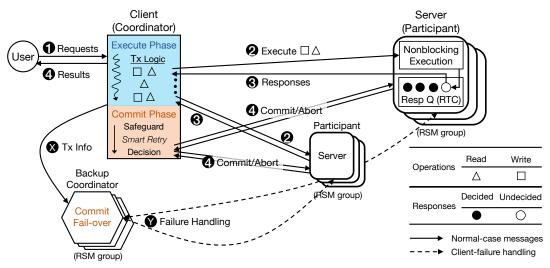

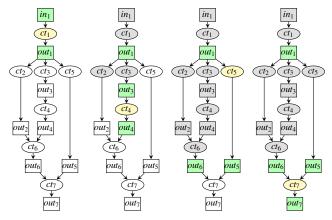

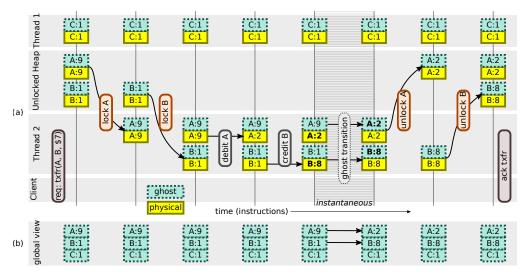

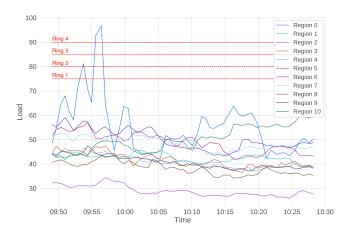

**Figure 2:** Lock and qnode structures of the TCLOCκ. (a) Initially, the lock is in the unlock state.  $t_1$  first switches from its main stack ( $M_1$ ) to the ephemeral stack ( $E_1$ ), and (b) joins the waiting queue. (c)  $t_1$  being at the head of the queue, becomes the combiner. Meanwhile,  $t_2$  and  $t_3$  join the queue. They also switch their stack to  $E_2$  and  $E_3$ , respectively. (d)  $t_1$  begins the combining process by traversing the queue and finds  $t_2$ . (e)  $t_1$  switches to  $t_2$ 's main stack ( $E_1 \rightarrow M_2$ ) and executes  $t_2$ 's critical section. (f) Once finished,  $t_1$  first switches back to  $E_1$  and then notifies  $t_2$  that  $t_1$  has finished executing its critical section. (g)  $t_2$  then switches back to  $M_2$  and exits its unlock phase. Meanwhile,  $t_1$  finds  $t_3$  as the last waiter. (h)  $t_1$  notifies  $t_3$  that it is now at the head of the queue, then  $t_1$  switches its stack to  $M_1$ , executes its critical section, and finally exits the unlock phase.

its critical section to the combiner. The waiter then busy-waits using the ephemeral stack while the combiner accesses the waiter's main stack to execute the critical section. Importantly, the use of an ephemeral stack does not introduce any new stack overflow bugs since it is a separate memory from the thread's execution stack. By incorporating the ephemeral stack, TCLocks maintain the single-writer principle, thereby preventing concurrent access and the corruption of waiters' stack.

#### 3.2 Spinlock: TCLock<sup>SP</sup>

TCLOCK<sup>SP</sup> augments the TAS and MCS lock by adopting the combining technique from MCS-style combining works [45, 47]. It involves a waiting thread becoming a combiner and batch waiters' requests up to a set threshold. Specifically, TCLOCK extends the DSM-Synch lock, using TAS as a top-level lock, and an MCS-style waiting queue for waiters. The waiter's queue node (qnode) maintains additional states: 1) request and wait flags for synchronizing between a waiter and the combiner and selecting the next combiner. 2) Socket ID for NUMA lock design (§3.6.3). 3) Batch count to limit

<sup>&</sup>lt;sup>1</sup>For example, the call instruction in x86.

excessive waiters, causing starvation or long-term fairness issues. And, 4) a pointer to the waiter's thread context for transparent delegation, which includes all registers and the stack pointer.

Transparent delegation invariants. Our lock algorithm maintains four invariants: 1) A combiner is always at the head of the waiting queue. 2) A waiter never uses its main stack while busy waiting. 3) All instructions in a critical section are executed only once, either by a waiter or the combiner executing on the waiter's behalf. 4) A combiner exclusively executes the waiter's critical section instructions defined between the lock and the unlock phase.

Workflow. Figure 2 presents a running example of  $TCLock^{SP}$ . Before requesting a lock, every thread executes in its main context (a). When a thread requests a lock, it switches to an ephemeral stack, saves its main context in its qnode, and joins the queue (b). Now, the head of the queue (t1) becomes the combiner, while other threads (t2 and t<sub>3</sub>) join the queue after switching to their respective ephemeral stacks. They wait for notification from the combiner, while processing any interrupts and signals on their ephemeral stacks. The combiner iterates through the queue and finds t2's request (d). t1 context-switches to t2's main context using t2's qnode, and starts executing t2's critical section (e). Reaching the unlock API of t2, t1 switches back to its ephemeral stack, notifies t2, and checks for other requests (f). Once t2 receives notification, it switches back to its main context, which now points to the end of the critical section. It then continues executing its non-critical section (g). Finally, the combiner iterates through the entire queue, it passes the combining role to t3, switches to its main context, and executes its critical section (h). Finally, t<sub>1</sub> unlocks the lock, allowing t<sub>3</sub> to acquire it and continue the combining process.

**Algorithm.** Listing 1 presents the TCLocκ<sup>SP</sup> pseudocode. A thread t first attempts to acquire the TAS lock on the fast path (line 17). On success, t executes its critical section directly. Otherwise, t finds its thread-local combining structure (line 21), saves its register state on the main stack, switches to the ephemeral stack, and begins the slow path (lines 26-27). The slow path comprises four phases: 1) t joins the queue and busy-waits locally. 2) t then waits to acquire the TAS lock after becoming the head of the queue. 3) After acquiring the TAS lock, t checks the combining conditions. 4) Finally, t combines waiters' critical sections.

*Phase 1: Busy-waiting phase.* Upon entering the slow path, t initializes its qnode (line 32). Specifically, it sets the wait field to True, request field to UNPRCSD, and the next pointer to None. The combiner notifies a waiter with the wait flag and uses the request flag to specify whether it executed a waiter's critical section. t then adds itself to the waiting queue by atomically swapping the tail with the qnode's address (line 36). After that, t checks for any preceding waiters

in the queue. If true, t joins the queue as a waiter (line 38) and waits for the combiner's notification (lines 39-40); otherwise, it proceeds to phase 2. While in the queue, t busywaits for the combiner to execute its critical section. After reaching the end of t's critical section, the combiner pushes the first instruction after the unlock API (line 107) on t's main stack. It then marks t's request as complete (i.e., PRCSD) (line 28), which switches to its main context and begins the non-critical section (line 107). If, however, t's request is not completed, t reaches the head of the queue and moves to phase 2.

Phase 2: Global lock acquisition phase. t now tries to acquire the TAS (global) lock using the CAS operation (lines 46-50). Phase 3: Combining-role decision phase. After acquiring the global lock, t checks whether it can be a combiner (lines 52-56). If t is the only one in the queue, it resets the queue tail, (lines 52-53), switches to its main stack (line 28), executes its critical section, and releases the lock. Otherwise, t checks if there are at least two waiters in the queue. If true, t proceeds to phase 4 as a combiner. Otherwise, t passes the combining role to the next waiter (lines 58-60) by setting the wait bit to false, and releases the lock after executing its critical section. Phase 4: Combining phase. t begins the combining phase by disabling the fast path, thereby forcing new waiters to join the queue (line 63). t iterates over the queue to execute each waiter's critical section (lines 65-75). Within the loop, t selects the next waiter (4a line 67), and records the waiter's information (qnode) in its thread-local combiner struct (cst) to later use it for resuming the combining process. Then t switches from its ephemeral stack to the waiter's main stack, and executes the waiter's critical section (4b line 70). Once finished, t notifies the waiter by first setting the request flag to PRCSD and resetting the wait flag (4c line 72). t continuously iterates until it reaches the combining threshold or cannot find two subsequent waiters in the queue (4d) lines 73-75). After exiting the loop, t ends the combining phase by changing the locking mode to the non-combining mode (line 77). t then notifies the next waiter to be the head of the queue (line 78), and finally executes its critical section.

During the unlock phase, t can be in one of the two states: G\_LOCKED: t unlocks the TAS lock by resetting its value and returns (lines 92-94). G LOCKED COMBINER: t does not release the TAS lock. It context switches from a waiter to the combiner by switching from the waiter's main stack to the combiner's ephemeral stack (lines 98) After switching, t resumes the combining loop and notifies the waiter about the completion of the critical section (line 72).

#### 3.3 Proof Sketch of Correctness

Mutual exclusion. TCLock ensures mutual exclusion by maintaining two invariants: First, only one thread can hold the global TAS lock, which can also be a combiner; Second, the main stack of a thread is active on only one thread at any time. TCLock piggybacks on the mutual exclusion property

```

1 PRCSD

= 0 # Waiter's request is processed by the combiner

# Phase 3: Combining-role decision: Whether to combine

51

UNPRCSD = 1 # Waiter's request is not processed until now

if CAS(&lock.tail. gnode. None) == gnode:

52

G_UNLOCK = 0, G_LOCKED = 1 # TAS known states

53

return # If only one in the queue, return

G_LOCKED_COMBINER = 2 # State to mark combining phase

qnext = qnode.next # Someone joined the queue; get qnode ptr

54

WAITERS_TO_COMBINE = 1024 # Combining batch count

while anext is None:

55

56

qnext = qnode.next

class thread local combiner struct:

# If there are at least two waiters, start combining

57

qcurr = None, qprev = None, qnext = None, node = init_node()

58

if gnext.next == None:

counter = 0, lock_addr = Array[None]

59

notify_next_queue_head(qnext) # next waiter is combiner

10

estack_rsp = init_ephemeral_stack()

60

return

11

61

# Phase 4: Combining: Batch requests with dynamic policies

12 class lock:

62

glock = 0. tail = None # TAS: top level lock, MCS queue

lock.glock = G_LOCKED_COMBINER # Declare combining phase

13

counter = 0

14

64

def spin lock(lock):

while True: # Combiner loop

15

65

qcurr = qnext # Get the very next waiter after combiner

16

# Fastpath: Try to acquire the TAS lock

66

if CAS(&lock.glock, G_UNLOCK, G_LOCKED) == G_UNLOCK:

qnext = select_next_waiter(qcurr) # 4a Get the next node

17

18

return # Got the lock, going to execute the critical section

cst.qcurr = qcurr # For qcurr's stack switch in unlock()

68

19

# 4b Combiner's ephemeral stack

ightarrow next waiter's stack

69

20

# Switch to the ephemeral stack and acquire the lock in slowpath

switch_stack_from_combiner_to_waiter(cst, qcurr)

21

cst = this_thread_comb_struct() # Get the per-CPU combiner struct

# Waiter's critical section execution finished

switch_stack(lock, cst) # Switch stack and begin slowpath function

22

notify_waiter(qnode) # 40 Mark as completed

23

return

if qnext is None or qnext.next is None or

73

24

counter >= WAITERS_TO_COMBINE: # 4d Check comb. cond.

74

def switch_stack(lock, cst):

break

75

{\tt switch\_to\_ephemeral\_stack(cst.node)} \ \textit{\# Main} \ \rightarrow \ \textit{ephemeral stack}

# Combiner phase is over, now combiner runs its CS

76

lock_slowpath(lock, cst)

lock.glock = G LOCKED # Reset TAS lock to normal lock

77

{\tt switch\_from\_ephemeral\_stack(cst.node)} \ \textit{\# Ephemeral} \ \rightarrow \ \textit{main stack}

notify_next_queue_head(qnext) # Next waiter is the combiner

30

def lock_slowpath(lock, cst):

Select the next node based on the policy, eg., NUMA etc.

80

qnode = cst.node # Get the pointer to qnode in the combiner struct

81

def select_next_waiter(qnode):

init_qnode(qnode, wait = True, request = UNPRCSD ,

return gnode.next

82

next = None, skt_id = numa_id()) # Initialize waiter's qnode

83

84 def notify_next_queue_head(qnode):

# Phase 1: Busy waiting: Join the queue and wait until notified

qnode.wait = False

85

qprev = SWAP(&lock.tail, &qnode) # Atomically add node to tail

if qprev is not None: # Waiters are already present in the queue

87 def notify_waiter(gnode):

qprev.next = qnode # Link qprev with qnode to form a queue

qnode.request = PRCSD

88

while qnode.wait is True:

qnode.wait = False

40

continue # Wait for the combiner to halt waiter's spinning

if qnode.request == PRCSD : # Waiter request has been processed

41

91 def spin unlock(lock):

return #Combiner executed my CS; jump to non critical section

42

if lock.glock == G_LOCKED:

92

43

lock.glock = G_UNLOCK # Only true for no combining phase

44

# Phase 2: Global lock acquisition: Acquire the TAS lock

94

return

# Waiter is at the head of the queue; get the TAS lock

45

# Jump back to combiner

95

while True: # Wait for the glock to be unlocked

46

96

cst = this_cpu_comb_struct()

while lock.glock != G_UNLOCK:

47

# Waiter's stack → combiner's ephemeral stack

48

continue

98

switch_stack_from_waiter_to_combiner(cst.qcurr, cst)

if CAS(&lock.glock, G_UNLOCK, G_LOCKED) == G_UNLOCK:

49

return

break # Got the TAS lock

50

· Main stack

for notification stack switch to non-CS

101

: Ephemeral stack

class main:

102

Line 41-42

Line 39-40

Line 99

Line 107

spin_lock(A)

Switch to

103

Line 28

Pass combiner

spin unlock:

104

instr1

Call

ephemeral

Start

Notify

role and

Execute

Phase 2

Phase 4: Start Jump to

Execute

Switch to

105

instr2

spin_lock

stack

switch stack

waiter's CS

slowpath

waiter

Phase 3

next waiter waiter's CS combiner stack

combining

spin_unlock(A)

106

Line 76-78

Line 103

Line 27

Line 25-26

Line 104-10

(111)

(V)

```

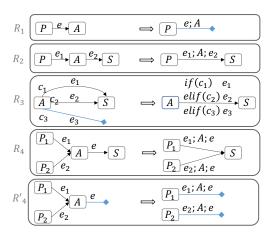

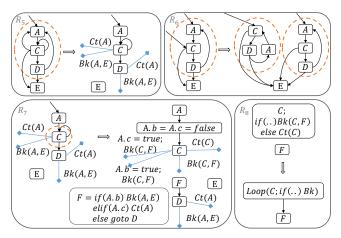

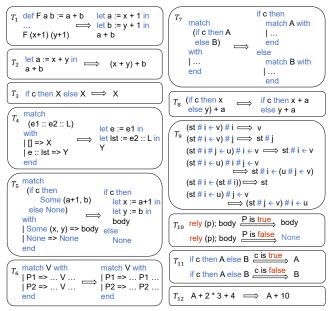

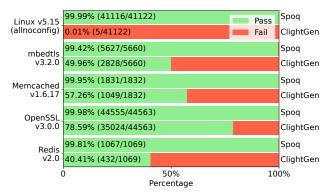

**Listing 1:** Pseudocode of TCLock along with the algorithm flow. In the bottom figure, Shade of the boxes show which stack is currently active and the numbers  $\mathbb{O}$ - $\mathbb{O}$  shows stack switching locations in the algorithm. At each of these locations, following return addresses are present on the outgoing stack:  $\mathbb{O}$  Outgoing: Waiters' main stack  $\rightarrow$  line 23.  $\mathbb{O}$  Outgoing: Combiner's ephemeral stack  $\rightarrow$  line 71.  $\mathbb{O}$  Outgoing: Waiter's main stack  $\rightarrow$  line 99.  $\mathbb{O}$  Outgoing: waiter's and combiner's ephemeral stack  $\rightarrow$  contents are discarded.

of the TAS lock as it uses atomic compare-and-swap (CAS) to guarantee thread exclusivity. Hence, thanks to the TAS lock, only one thread can hold the global lock at any given point and only one thread can access shared data at a time. Finally, our transparent delegation invariants ensure that a waiter never touches its own main stack while waiting for a combiner's notification. Moreover, TCLock ensures that

the switch from the waiter's main stack to the combiner's ephemeral stack (line 98) occurs at the end of the critical section, *i.e.*, at the end of the unlock function. Thus, after the waiter restores its context from the main stack (line 28), it never enters its critical section.

**Correct thread state.** TCLOCK preserves the correct waiter's state using a lightweight context switch mechanism

and avoids concurrent stack modification. Specifically, a waiter yields ownership of its main stack (line 26) before joining the waiting queue (line 36). Thus, a combiner thread can only obtain the ownership of a waiter thread's main stack after the waiter gives up the ownership. Finally, the combiner thread concedes its ownership of the waiter's main stack (line 98) before notifying the waiter (line 72). Therefore, our approach ensures that when a waiter reacquires the ownership of its main stack (line 28), the combiner is not using that stack.

#### 3.4 Blocking Lock: $TCLock^B$

$TCLock^B$  follows a similar design philosophy of the blocking SHFLLOCK, where waiters use the spin-then-park strategy. In this approach, a waiter spins locally until its time quota expires. Upon expiration, it schedules itself out if the system is oversubscribed; otherwise, it yields to the scheduler, which eventually reschedules the waiter. In addition, the lock queue maintains both active and passive waiters.

We design  $\mathsf{TCLock}^B$  by augmenting  $\mathsf{TCLock}^{SP}$  to support the parking/wakeup policy. We extend the combiner's role, which now wakes up sleeping waiters while executing their critical sections. The use of an ephemeral stack becomes critical for  $TCLock^B$  because parking of waiters requires calling a function, which pushes the function frame on the waiter's stack. Hence,  $TCLock^B$  uses the thread-local ephemeral stack to prevent concurrent accesses. The stack switching protocol remains the same as in TCLock SP. To enable efficient parking and wakeup, we add two new states to the request field of the qnode: PARKED, in which a waiter is scheduled out, and PRCSING, which indicates that the combiner has started executing a waiter's critical section.

In the slow-path phase, while spinning locally (i.e., phase 1), a waiter t checks if its time quota is up. If so, t attempts to park itself out. Specifically, t tries to change its request field from UNPRCSD to PARKED atomically. If successful, t parks itself out; otherwise, it continues spinning as the combiner has changed t's state. In phase 4c, while selecting the next head of the queue (notify\_next\_queue\_head()), the combiner atomically swaps t's state to PRCSING to prevent the waiter from going to sleep. Furthermore, after executing the critical section, the combiner atomically swaps t's state to PRCSD. In both cases, the combiner checks the old state of the request field. If it is PARKED, the combiner wakes up t. We use atomic instructions for changing the state to prevent the lost wakeup problem.

#### 3.5 Readers-writer Version: TCLock<sup>RW</sup>

TCLock<sup>RW</sup> is a combining-aware readers-writer lock that allows readers to execute in parallel, while writers are combined. TCLock uses a phase-based mechanism [35, 36] that alternates between readers and combined writers. TCLock<sup>RW</sup> comprises the following: 1) A counter that includes the reader count (RCNT), writer present byte (WP) to indicate if a writer is holding the lock, and writer waiting

```

1 RCNT = 1 \ll 16; WW = 0x100; WP = 0x1;

WCOMBINER = G_LOCKED_COMBINER

class rwlock: (32 byte lock)

# rwcounter → [RCNT: 17-63; WW: 8-16; WP: 0-7]

rwcounter = 0 # 8-byte readers-writer rwcounter

tail = None # Writers enqueue in this queue

wlock: mutex # Coordinate bw readers & first writer

def down read(rwlock): # Acquire read lock

atomic_inc(&rwlock.rwcounter, RCNT) # Increment reader count

if !(rwlock.rwcounter & Oxffff): # Check the first two bytes

12

return # Lock acquired, if writer not present or waiting

atomic_dec(&rwlock.rwcounter, RCNT) # Decrement reader count

read_lock_slowpath(rwlock) # execute read slowpath

14

16 def read_lock_slowpath(rwlock):

mutex lock(&rwlock.wlock) # Acquire mutex

atomic_inc(&rwlock.rwcounter, RCNT) # Increment reader count

18

while (rwlock.rwcounter & 0xfffff) > 0: # Check first two bytes

continue # Wait for writer to finish

20

mutex_unlock(&rwlock.wlock) # Release the mutex

21

22

def up_read(rwlock): # Release read lock

23

atomic_dec(&rwlock.rwcounter, RCNT) # Decrease reader count

24

def down_write(rwlock): # Acquire write lock

26

# The writer tries to set the WP byte (as 1)

if CAS(&rwlock.rwcounter, 0, WP) == 0:

return # Writer fastpath

30

# Switch to the ephemeral stack and acquire lock in slowpath.

cst = this_cpu_comb_struct() # Get the per-CPU comb struct

switch_stack(rwlock, cst)

35 def lock_slowpath(lock, cst): # Write lock slowpath

# Waiter

ightarrow queue's head; get the TAS lock

while True: # Wait for the glock to be unlocked

while lock.glock != G_UNLOCK:

40 -

if CAS(&lock.glock, G_UNLOCK, G_LOCKED) == G_UNLOCK:

break # Got the TAS lock

43

44 +

# Replace spinning on glock with rwcounter

mutex_lock(&lock.wlock) # Acquire mutex

45 +

46 +

if CAS(&lock.rwcounter, 0, WP) == 0:

47 +

goto unlock # Success if no readers are present.

48

49 +

atomic_inc(&lock.rwcounter, WW) # Indicate writer waiting

50 +

while True: # Spin until all readers finish CS

if CAS(&lock.rwcounter, WW, WP) == WW:

51 +

52 +

break

53 +

54 + mutex_unlock(&lock.wlock) # Release mutex

# MCS unlock phase

55

56

57

# Now, gnext is the combiner, indicated by glock word

58 -

lock.glock = G_LOCKED_COMBINER

59 -

# Now, gnext is the combiner, indicated by rwcounter word

60 +

lock.rwcounter = WCOMBINER

61 +

62

# Combiner phase is over, now combiner will run its CS

63 -

lock.glock = G_LOCKED # Reset TAS lock to normal lock

64 -

65 +

lock.rwcounter = WP

66

67 def up_writer(rwlock): # Release write lock

68 + if rwlock.rwcounter == WP:

69

rwlock.rwcounter = 0

```

**Listing 2:** Pseudo-code for  $TCLock^{RW}$ .

byte (WW) indicating a writer waiting to acquire the lock. 2) A writer queue (tail) for combining and parking waiting writers. This queue is similar to our  $TCLock^B$ 's queue. 3) A mutex, called wlock, that synchronizes the phase between readers and the head of the writers queue. Hence, wlock handles the parking of readers and the head of the write queue. We use the ShflLock<sup>B</sup> algorithm [52]—a traditional NUMA-aware queue-based mutex—for wlock than  $TCLock^B$ because maintaining a centralized count of readers (shared data) contradicts the design of combining that tries to localize the access to the shared data.

Algorithm. Listing 2 shows the necessary changes to  $TCLock^{SP}$ . A reader first atomically increments RCNT and executes its critical section if no writer is present (lines 10-11). Otherwise, it decreases the RCNT (line 13), and enters the slow-path phase. The reader first acquires wlock (line 17), it then increments the RCNT (line 18) to mark that a reader phase should begin soon, and waits for existing writers to exit (line 20). Finally, it unlocks wlock (line 21) and executes its critical section. In the unlock phase, a reader releases the lock by atomically decreasing RCNT (line 24).

A writer enters the critical section if it successfully switches WP from 0 to 1 (line 28). Otherwise, it switches to the ephemeral stack and begins the slow path phase (line 33). This slow path follows the same protocol as  $TCLock^{SP}$  except that the head of the waiting queue (line 44) acquires the wlock (line 45). After acquiring wlock, the writer tries to enter the critical section by atomically setting the value to WP (line 46). On failure, it sets the WW byte to 1 to prevent new readers from entering the critical section (line 49) and waits for other readers to leave. Once they leave, the writer atomically modifies the rwcounter from WW to WP (line 50-52), releases wlock, and starts the combining process. In the unlock phase, a writer resets the rwcounter to 0 if the value is WP.

#### 3.6 Optimizations

We propose three key optimizations to minimize further the data movement between the combiner and a waiter, and the cache-line bouncing of the lock word.

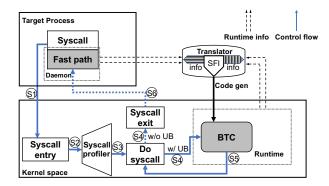

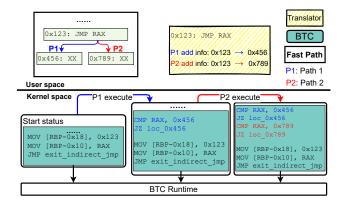

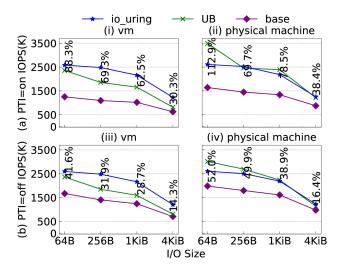

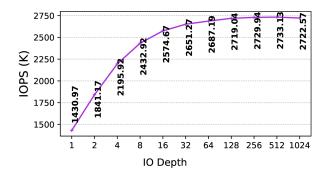

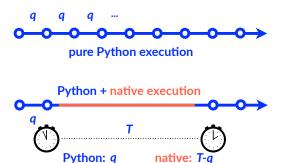

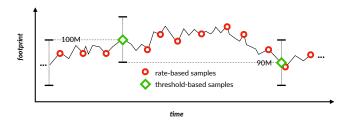

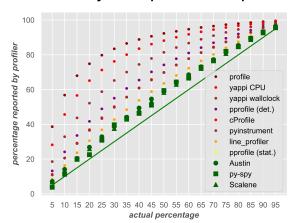

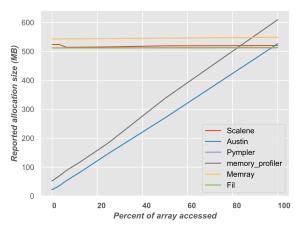

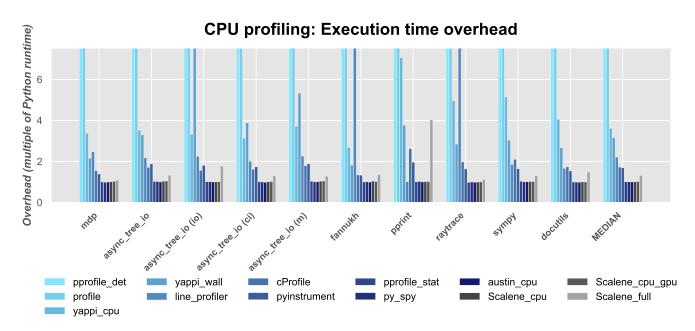

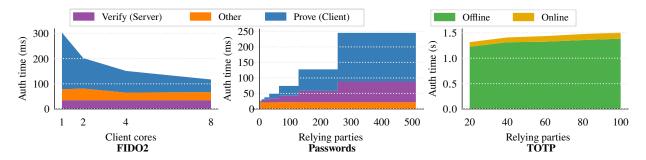

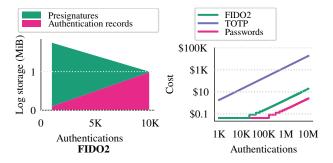

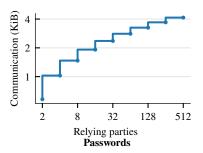

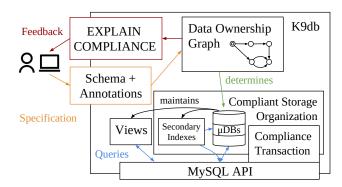

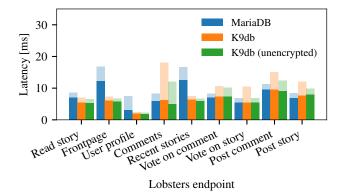

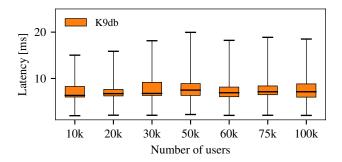

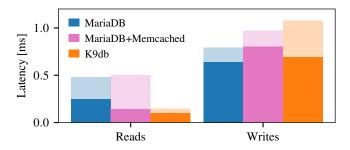

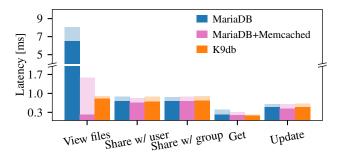

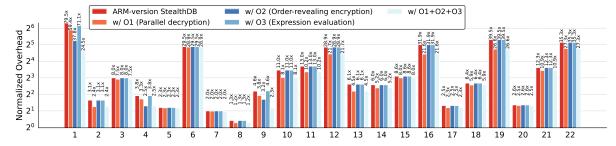

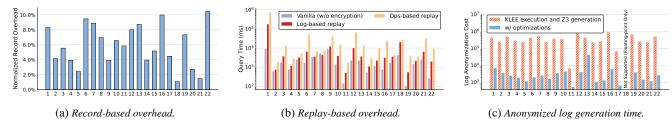

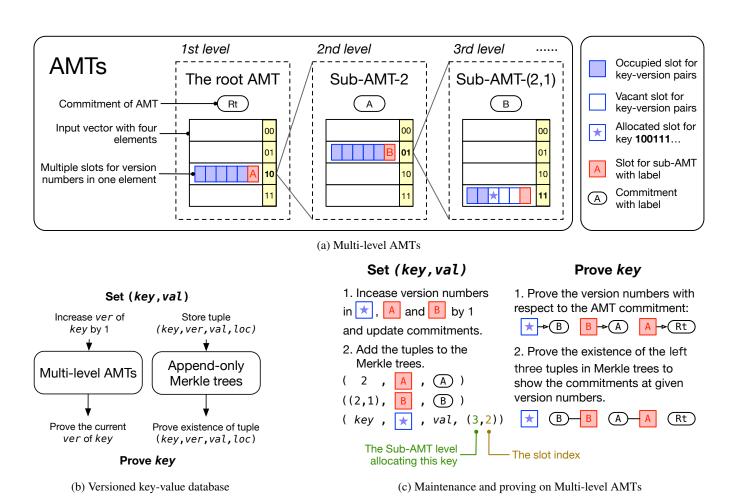

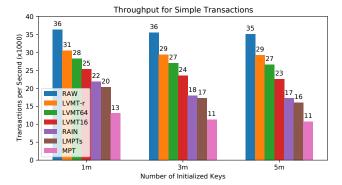

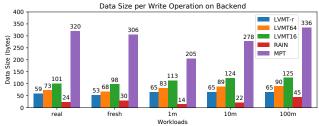

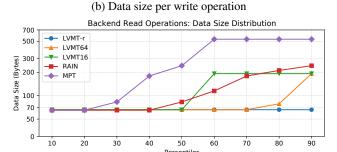

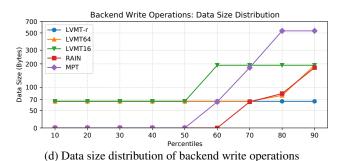

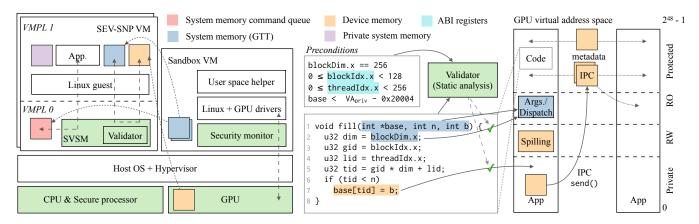

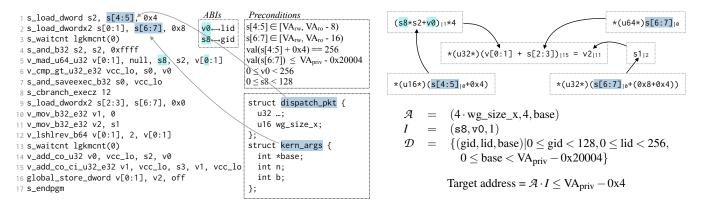

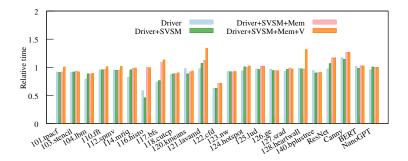

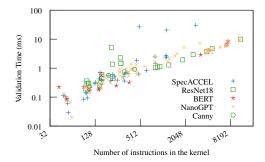

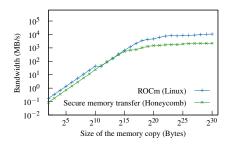

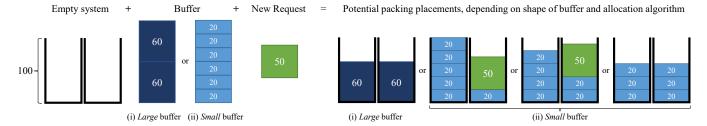

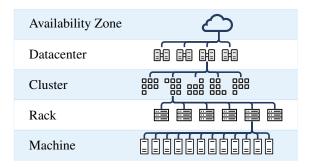

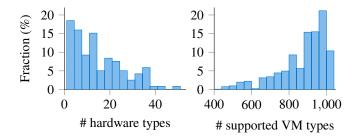

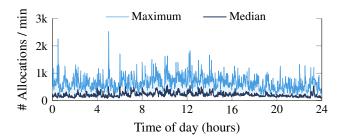

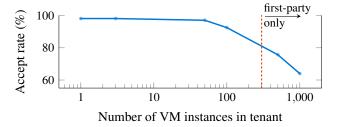

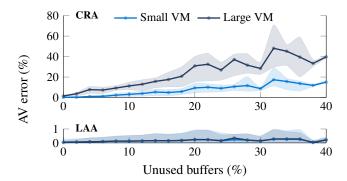

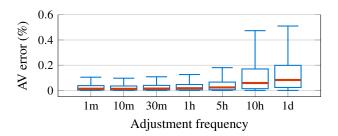

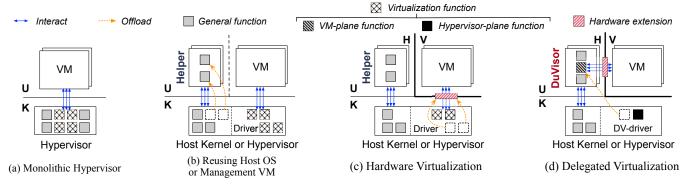

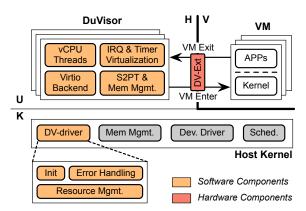

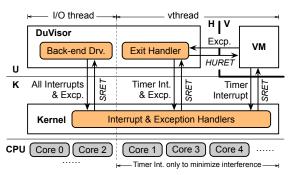

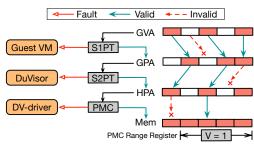

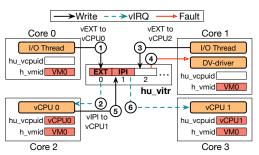

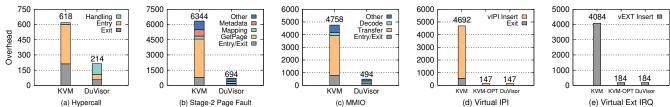

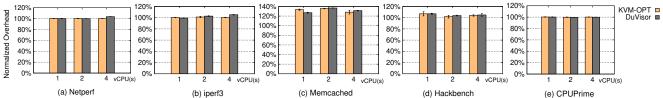

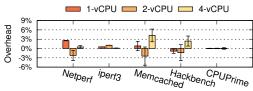

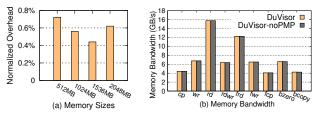

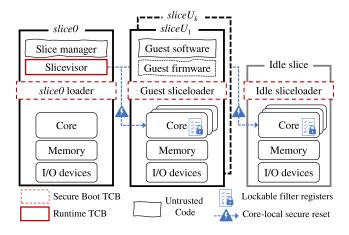

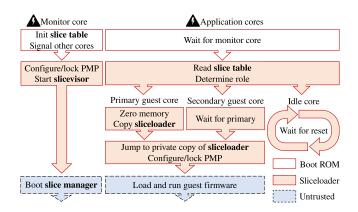

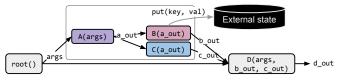

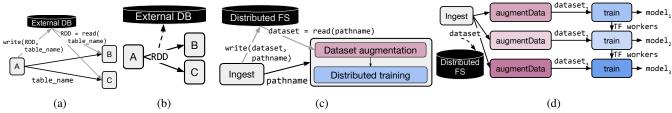

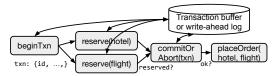

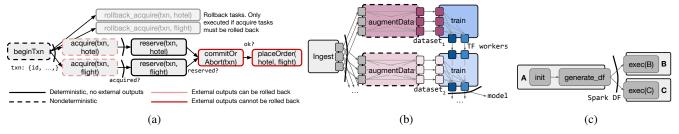

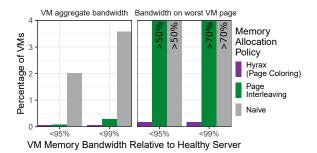

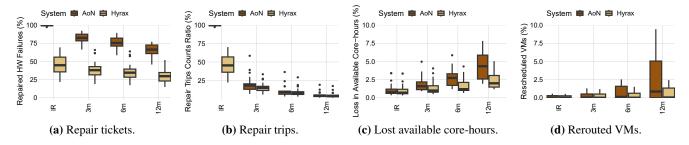

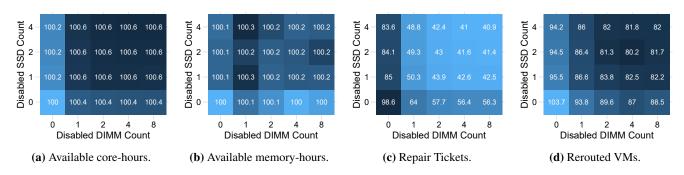

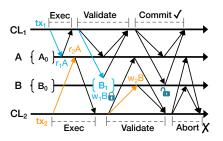

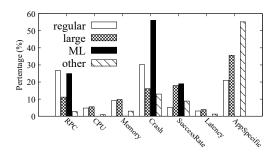

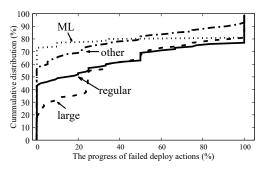

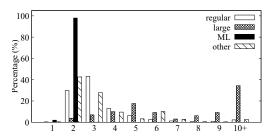

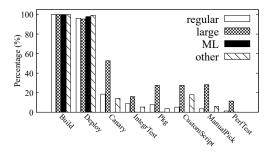

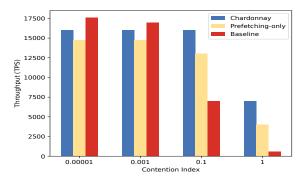

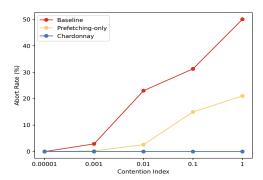

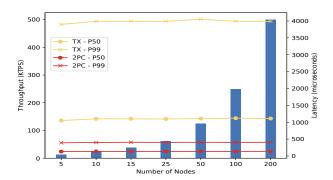

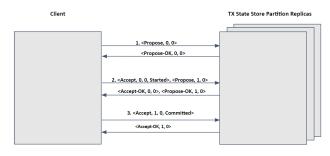

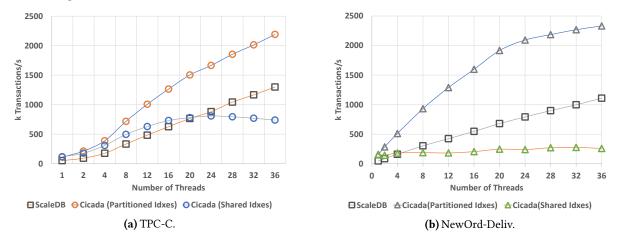

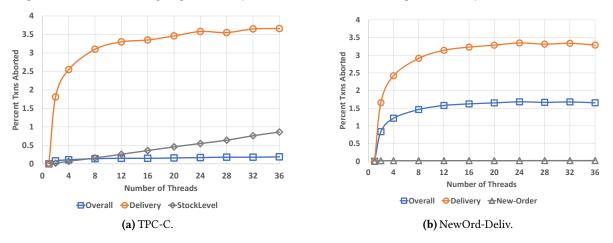

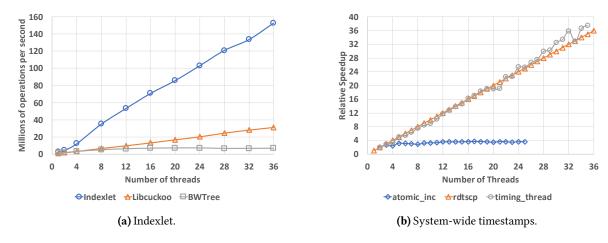

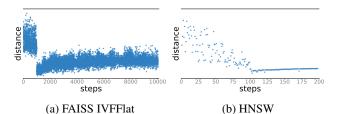

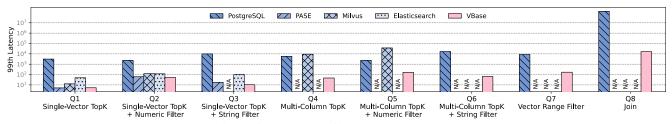

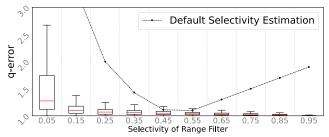

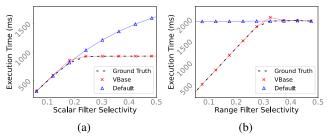

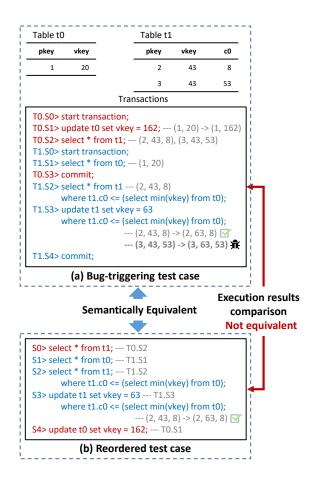

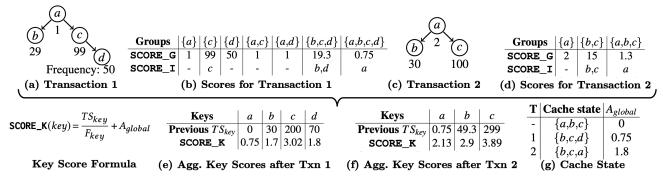

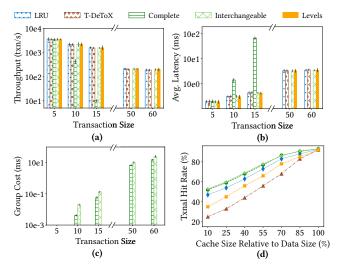

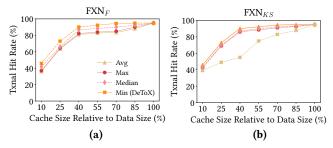

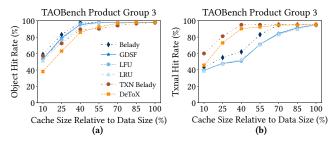

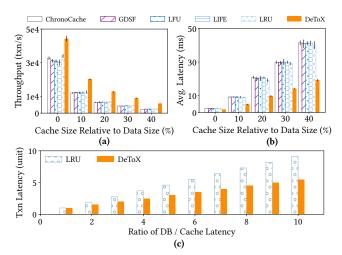

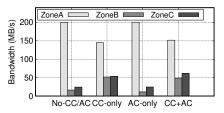

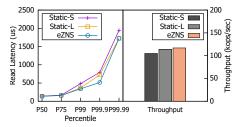

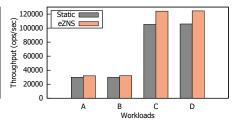

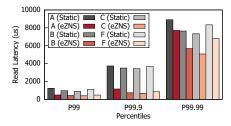

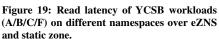

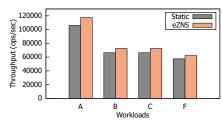

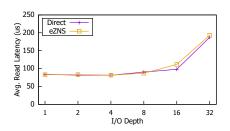

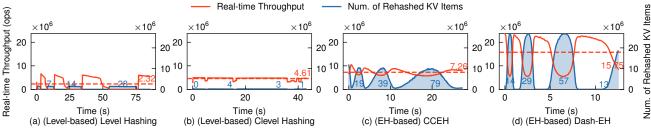

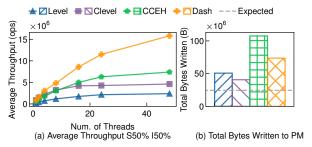

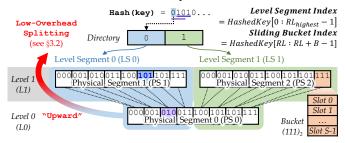

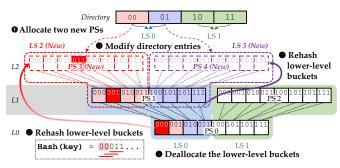

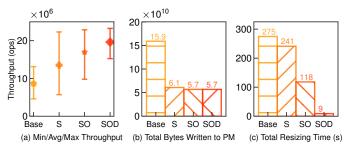

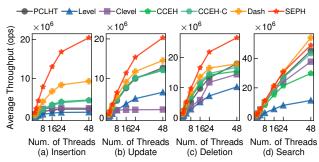

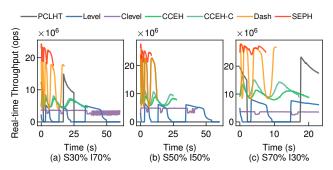

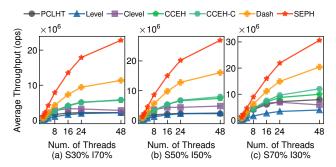

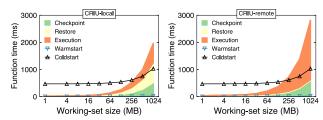

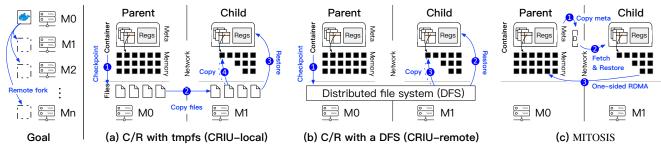

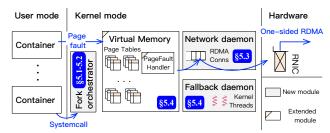

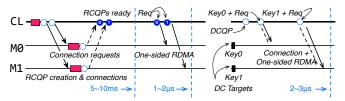

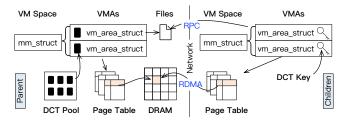

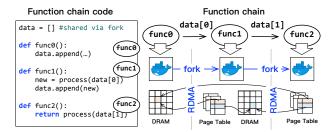

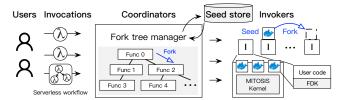

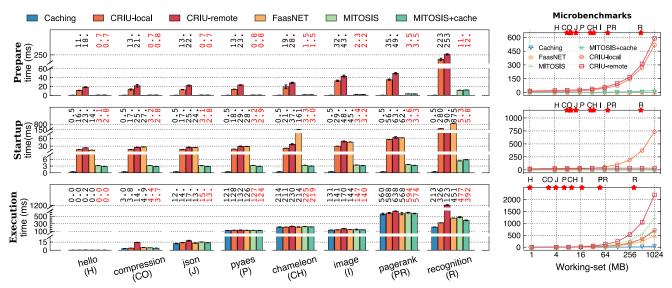

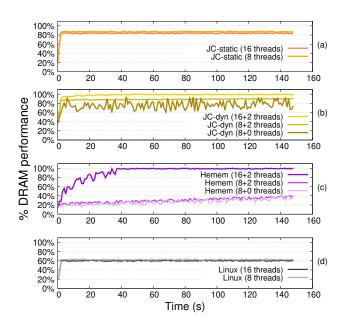

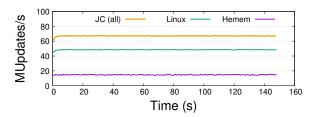

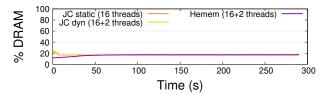

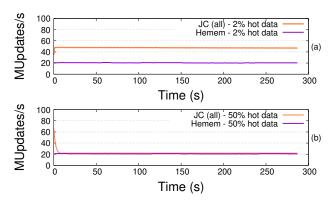

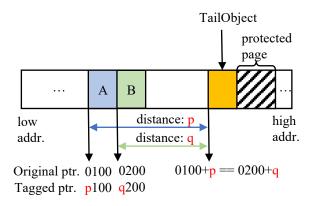

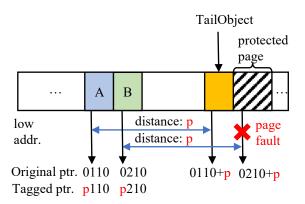

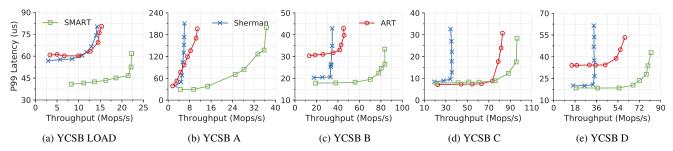

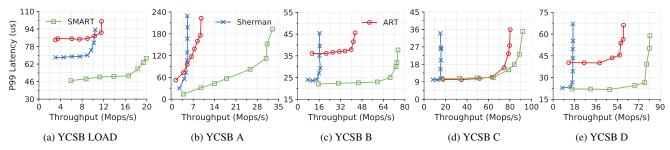

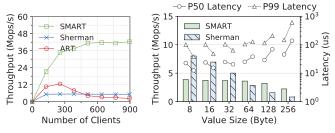

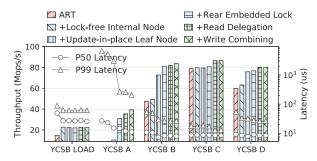

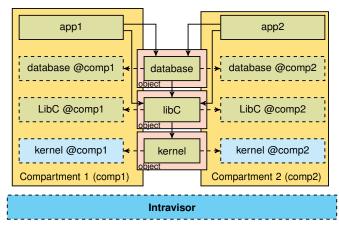

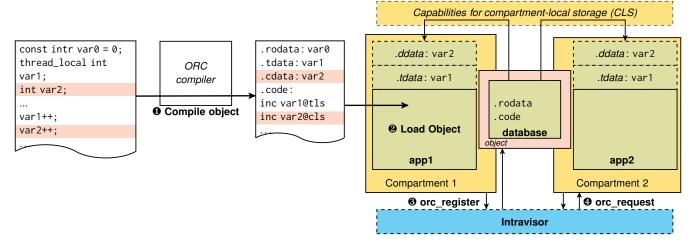

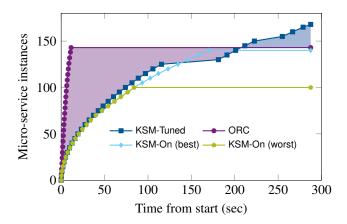

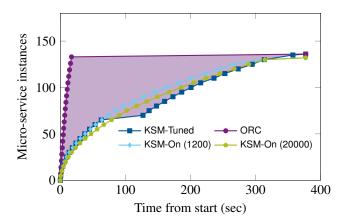

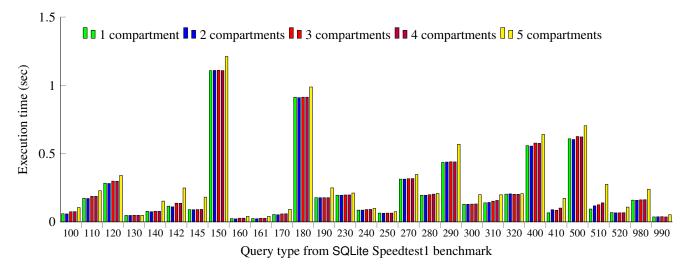

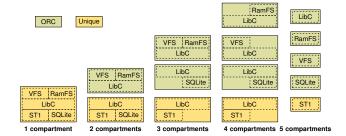

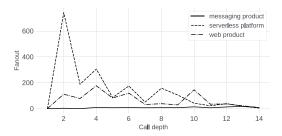

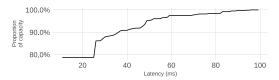

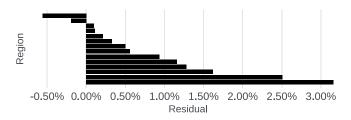

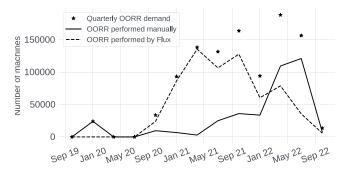

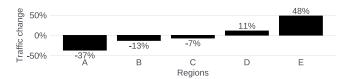

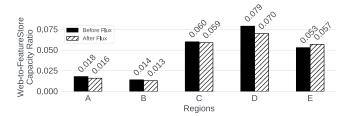

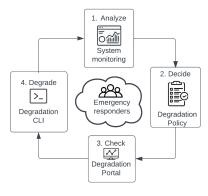

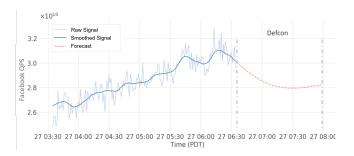

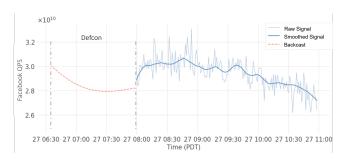

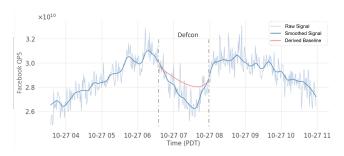

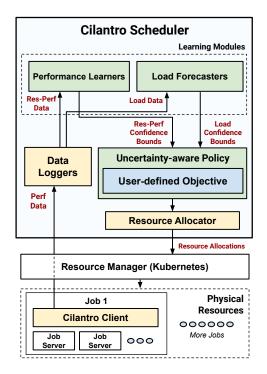

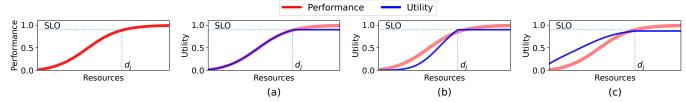

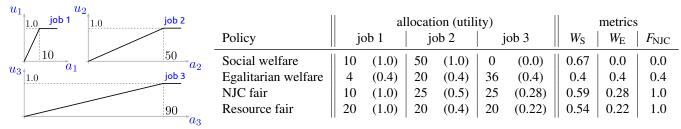

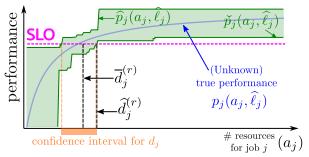

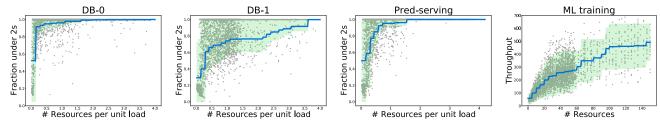

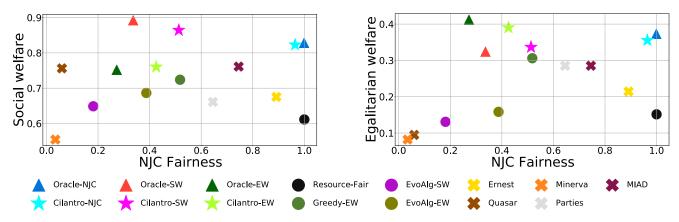

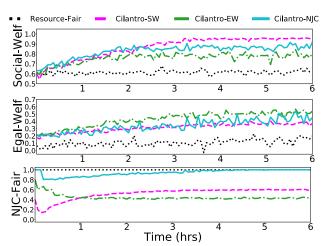

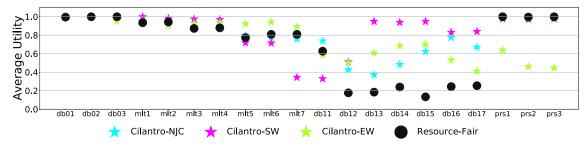

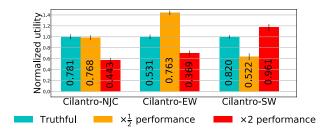

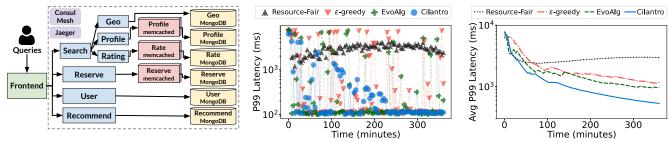

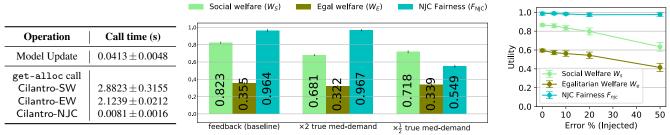

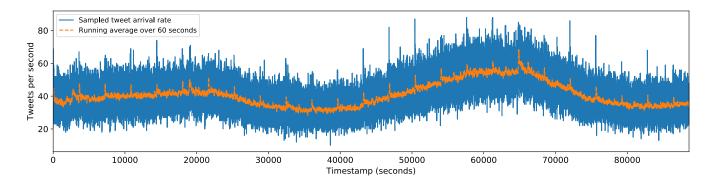

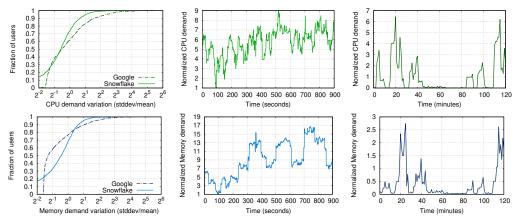

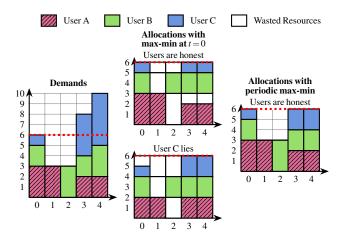

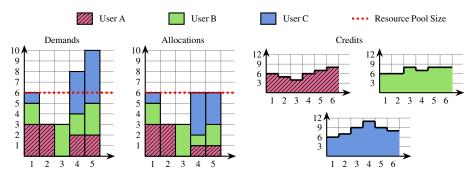

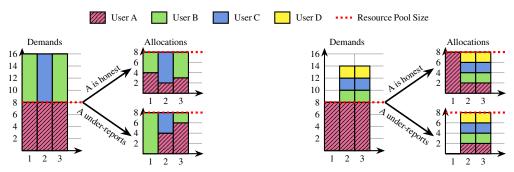

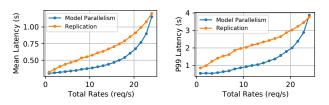

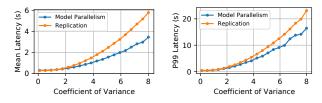

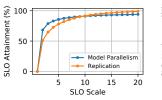

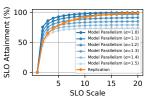

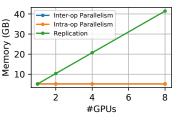

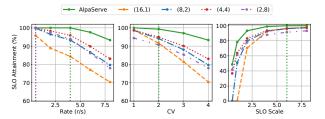

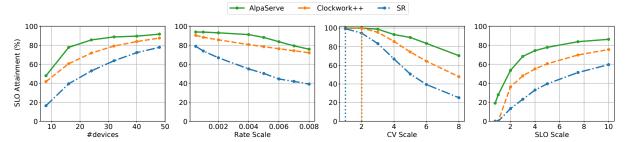

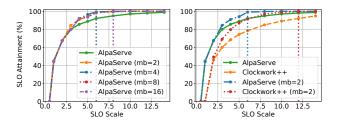

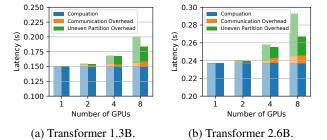

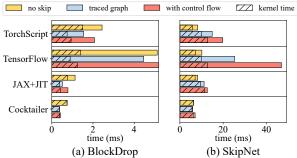

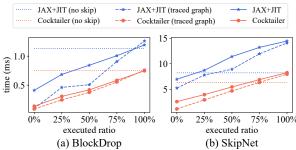

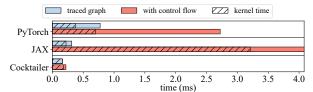

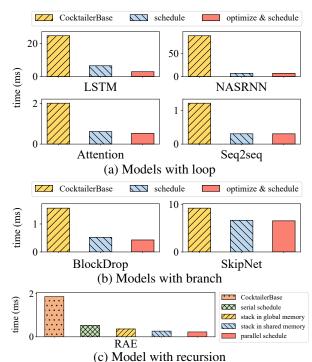

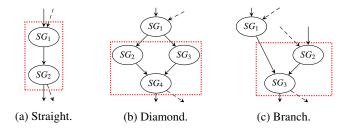

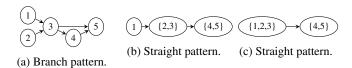

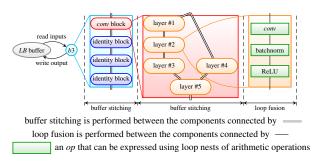

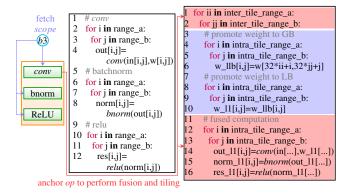

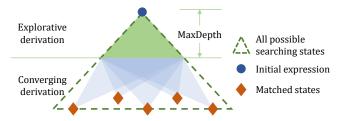

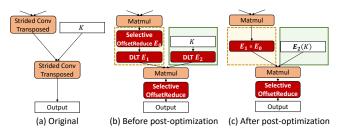

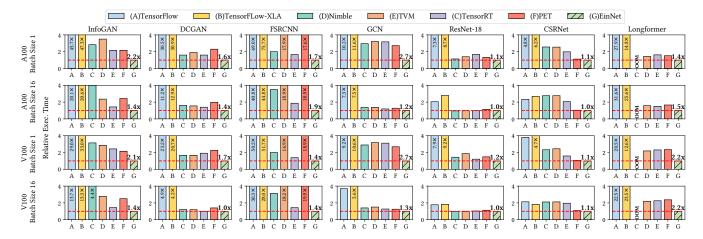

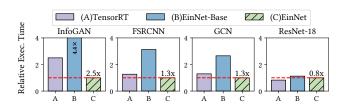

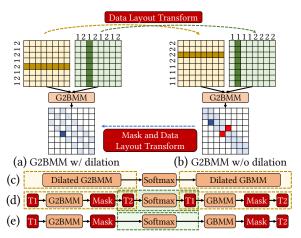

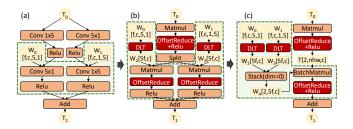

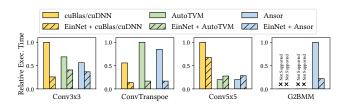

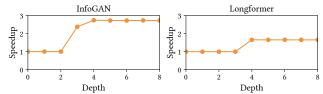

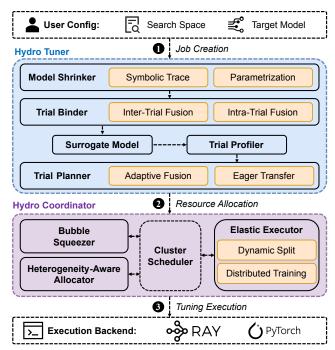

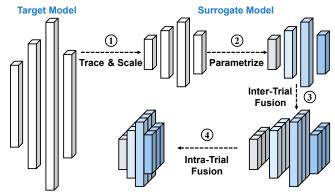

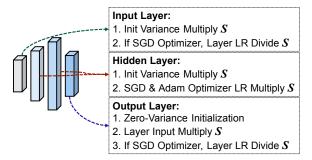

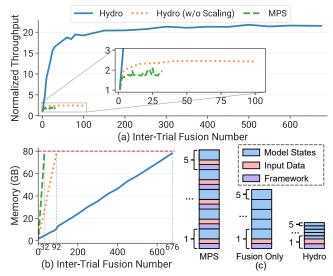

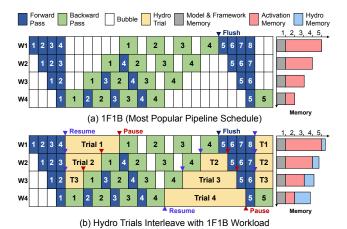

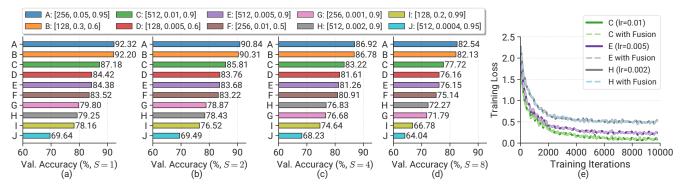

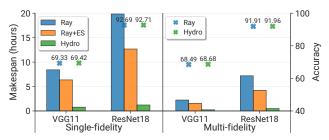

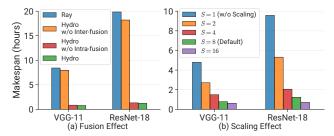

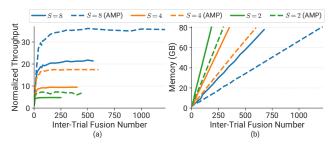

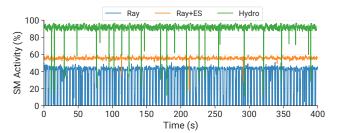

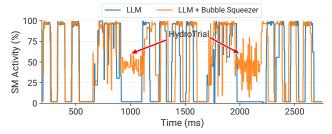

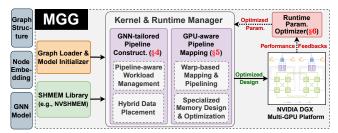

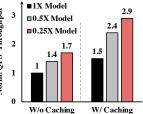

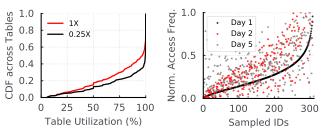

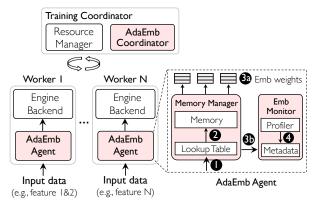

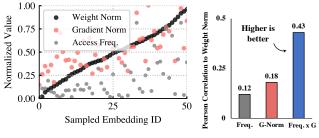

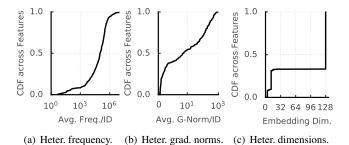

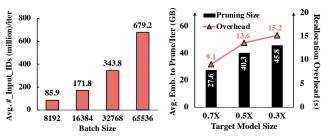

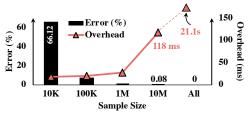

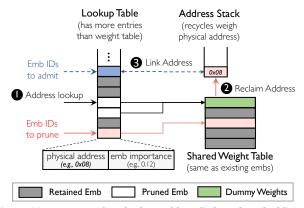

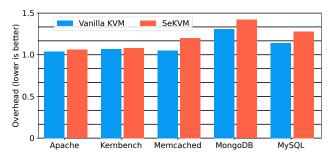

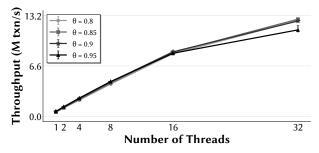

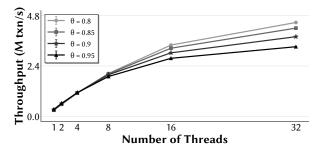

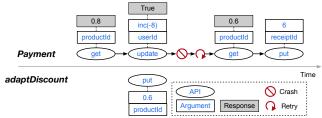

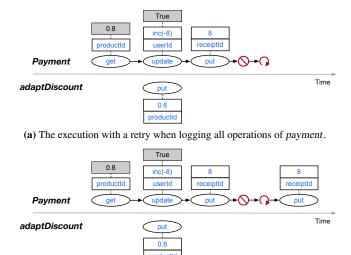

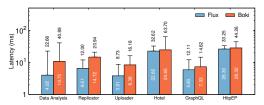

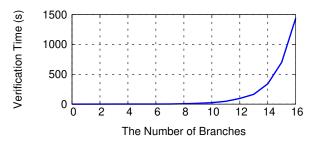

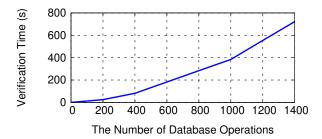

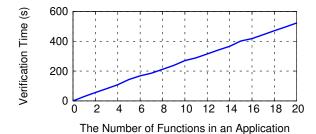

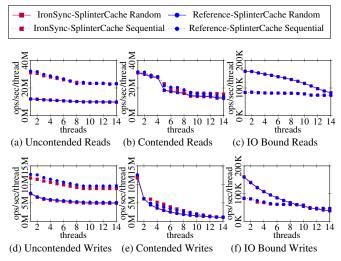

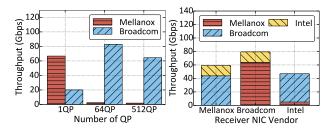

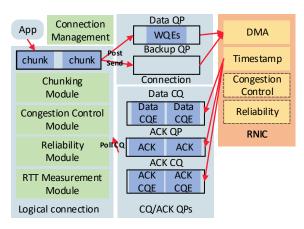

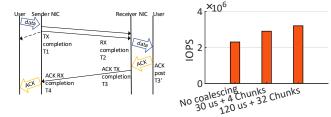

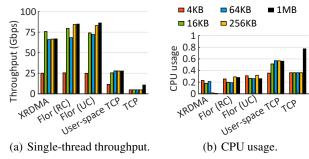

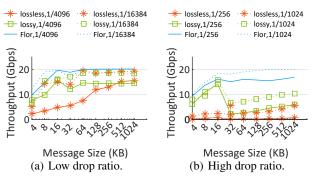

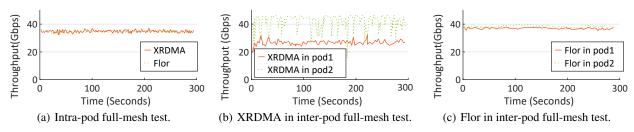

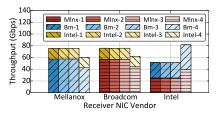

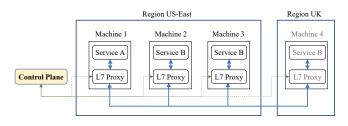

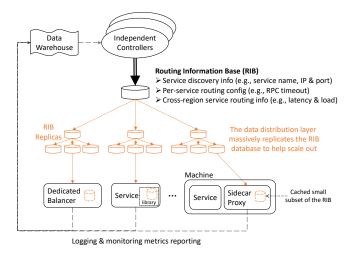

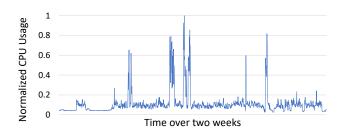

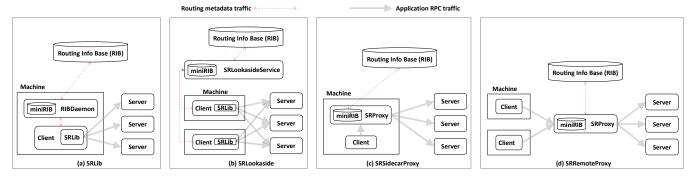

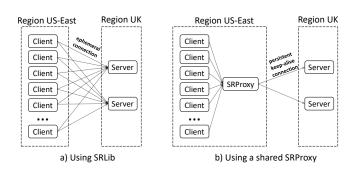

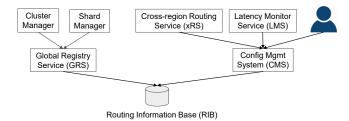

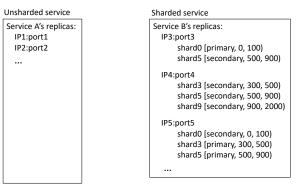

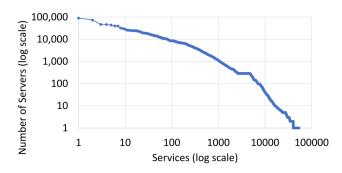

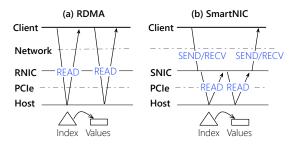

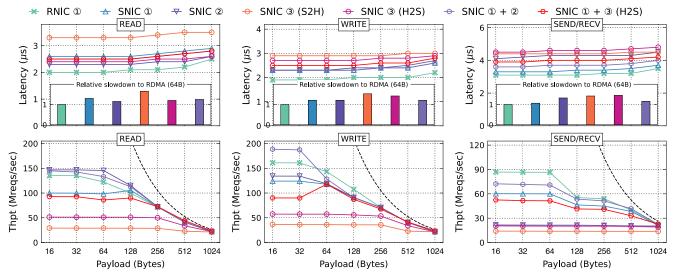

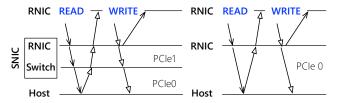

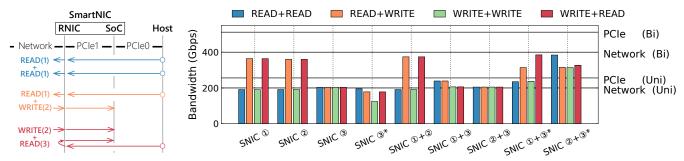

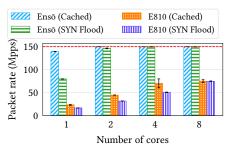

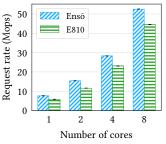

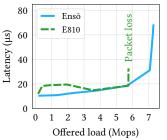

#### 3.6.1 Direct stack switching: waiter $\rightarrow$ waiter