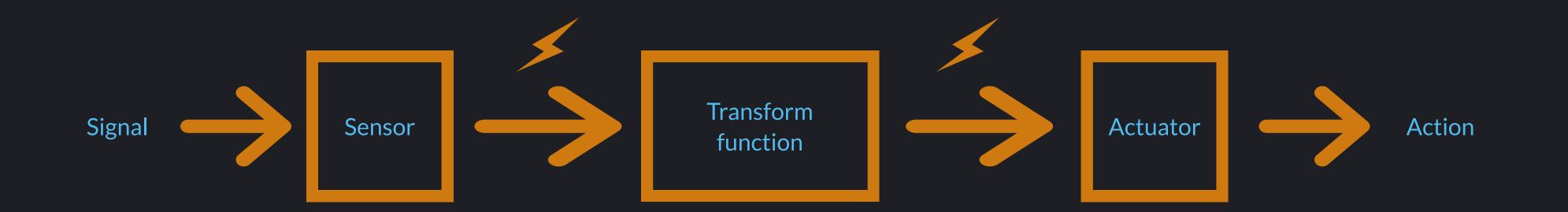

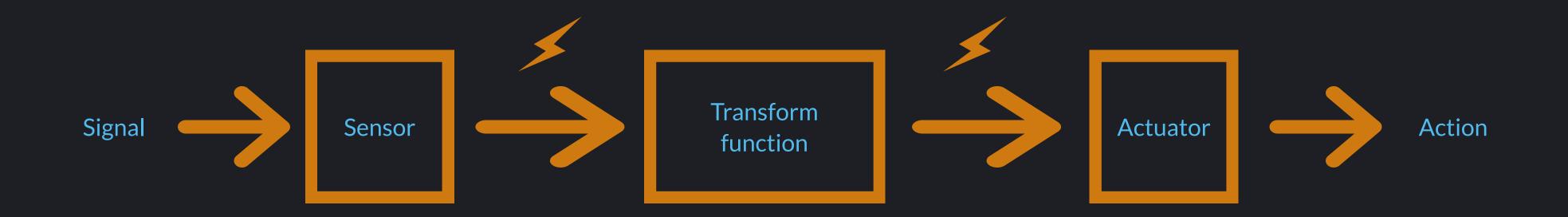

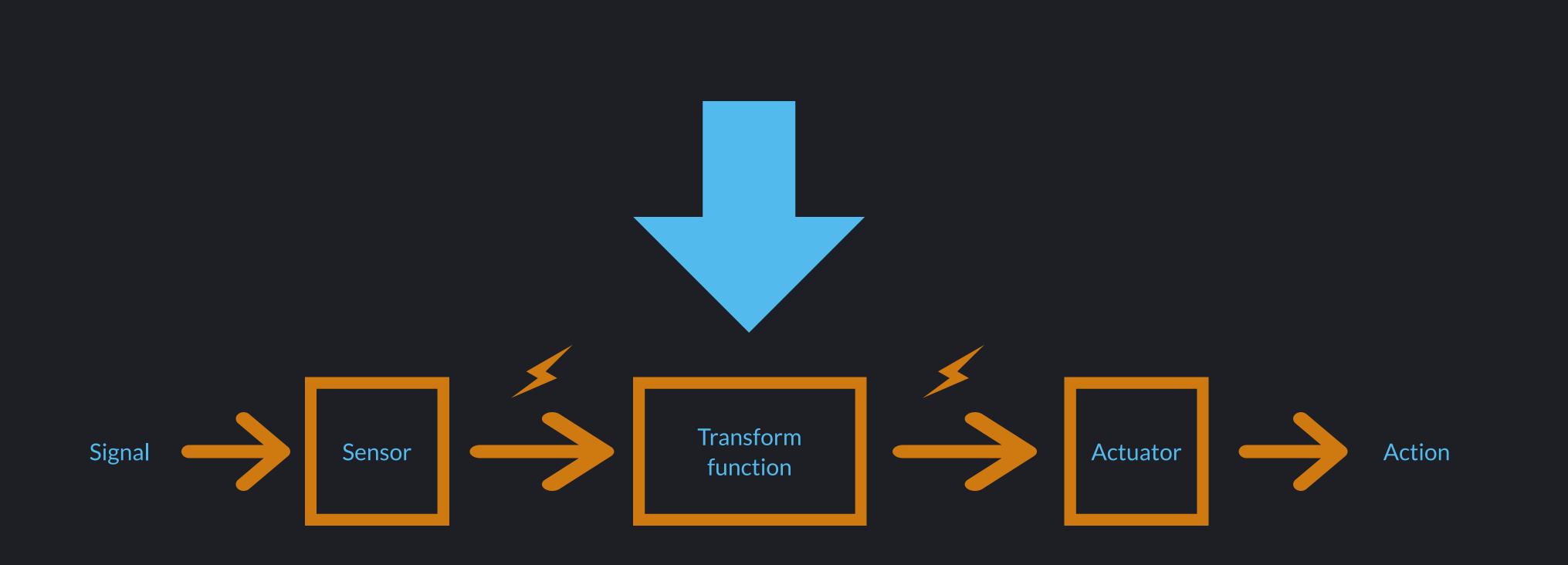

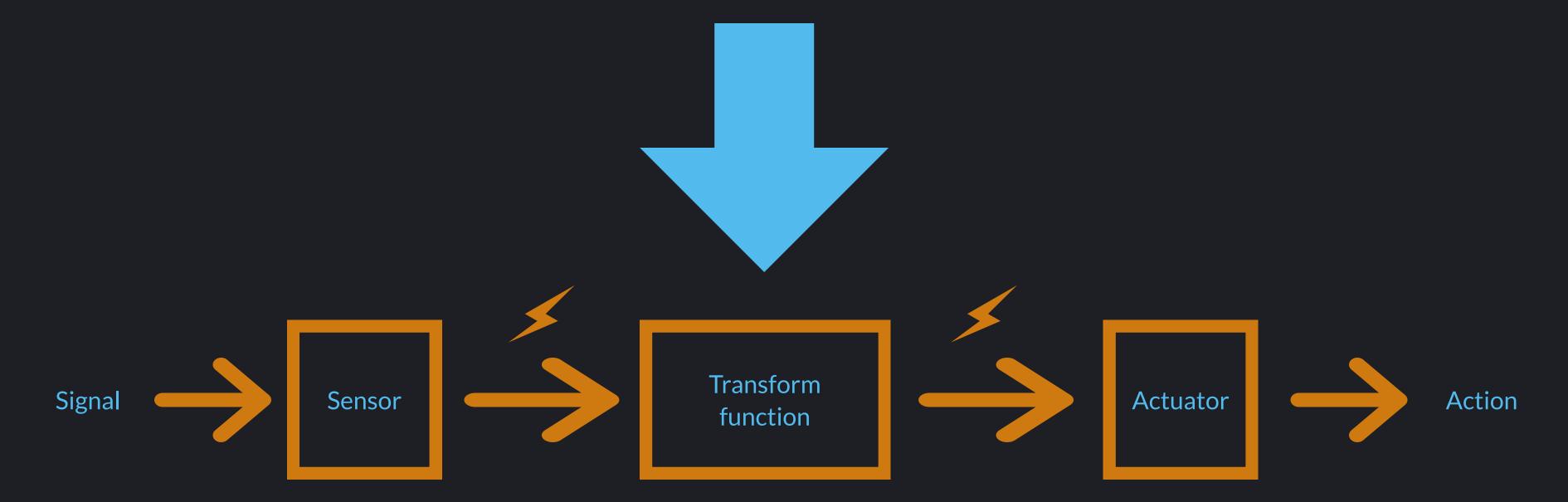

#### Transform function

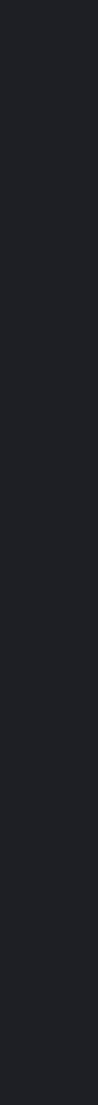

credit: Foone, https://twitter.com/Foone

credit: Foone, https://twitter.com/Foone

credit: Foone, https://twitter.com/Foone

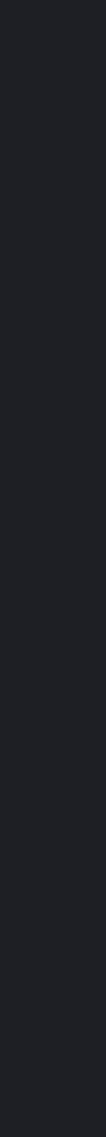

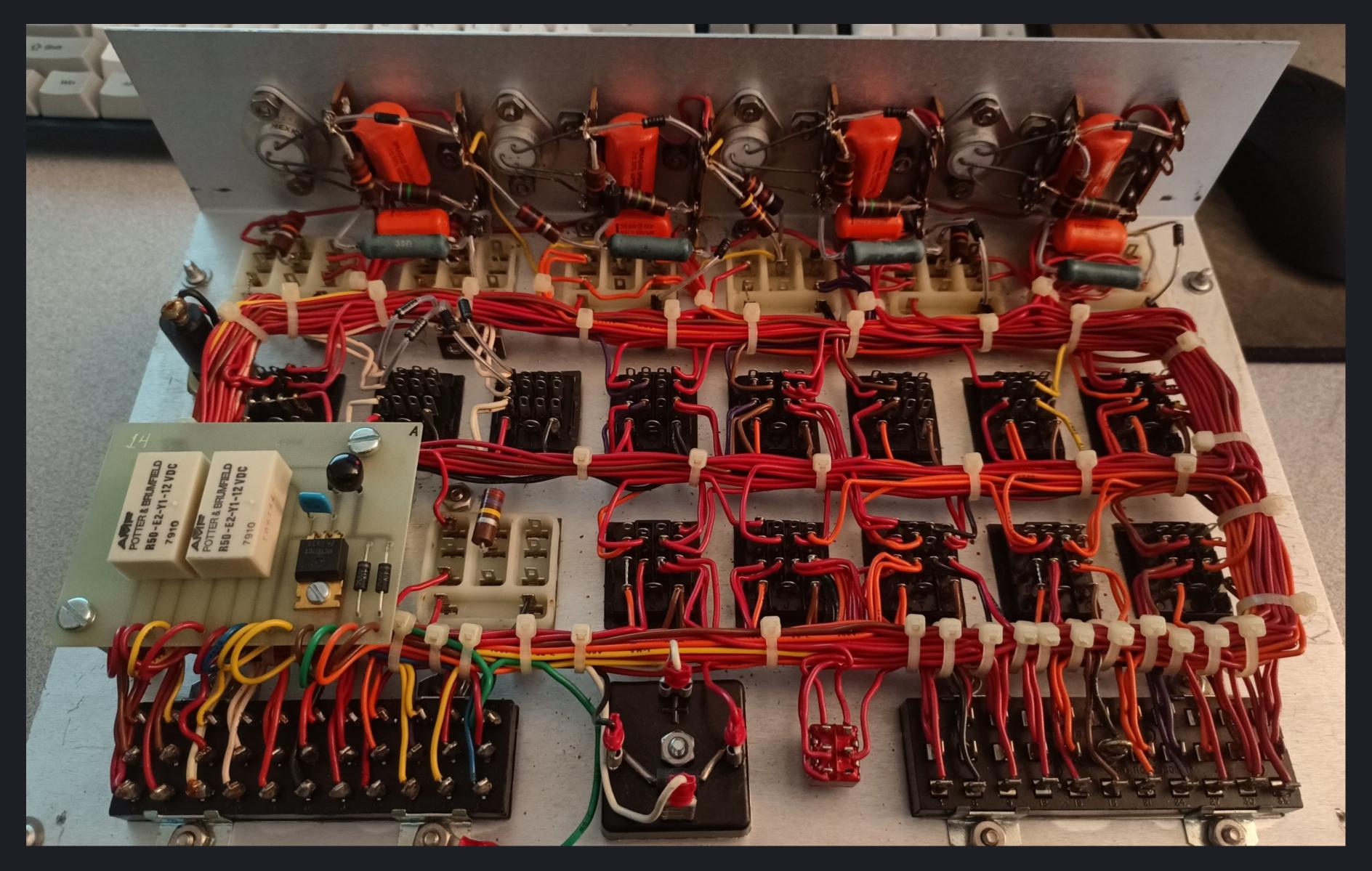

#### Modules with well known input/output relationship

credit: Foone, https://twitter.com/Foone

#### Modules with well known input/output relationship

• Well known composition functions

credit: Foone, https://twitter.com/Foone

• Well known composition functions

"just plumbing signals between these"

- Modules with well known input/output relationship

credit: Foone, https://twitter.com/Foone

- Modules with well known input/output relationship

- Well known composition functions

10

Oh

- "just plumbing signals between these"

- Easy to debug, the "real" signal can always be probed

credit: Foone, https://twitter.com/Foone

# Why not do everything like that ?

credit: Foone, https://twitter.com/Foone

credit: Foone, https://twitter.com/Foone

Noise

705

(O)

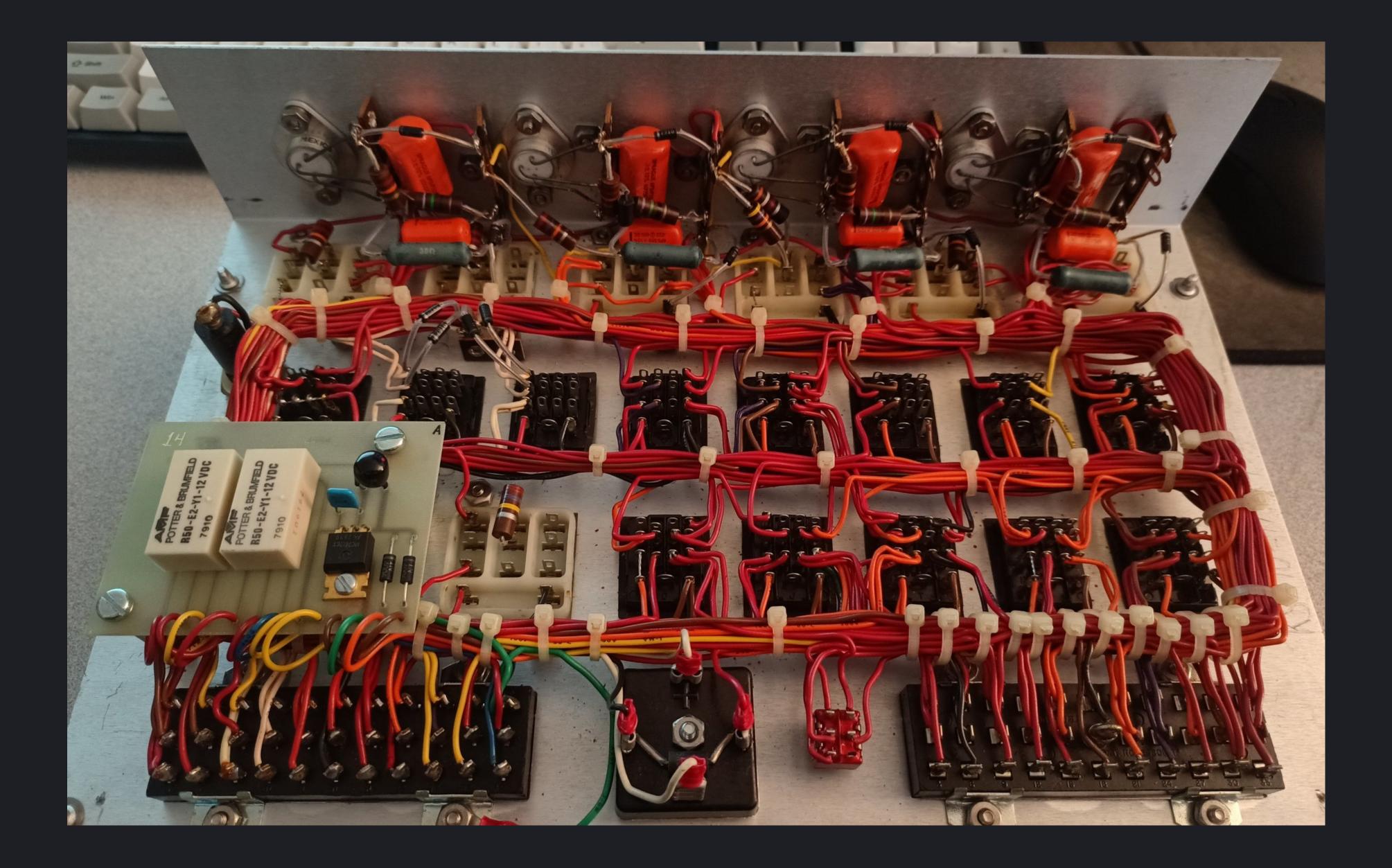

• Lot of specific components

Complex supply chain

Expensive (\$\$)

credit: Foone, https://twitter.com/Foone

10

Noise

101

On

Lot of specific components

Complex supply chain

Expensive (\$\$)

• Really slow design cycles (\$\$)

credit: Foone, https://twitter.com/Foone

10

### What if this was a reusable component we could adapt on the fly

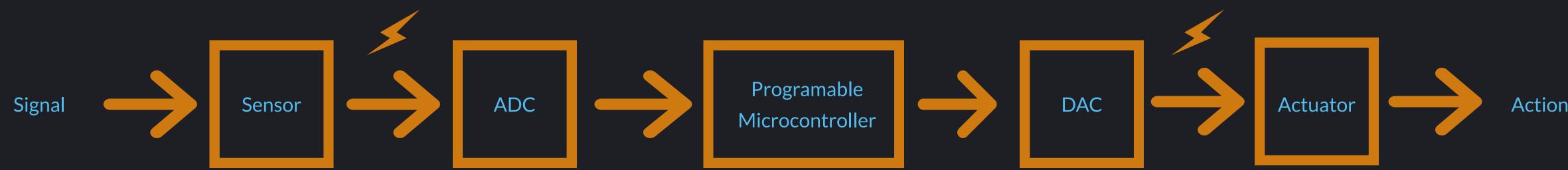

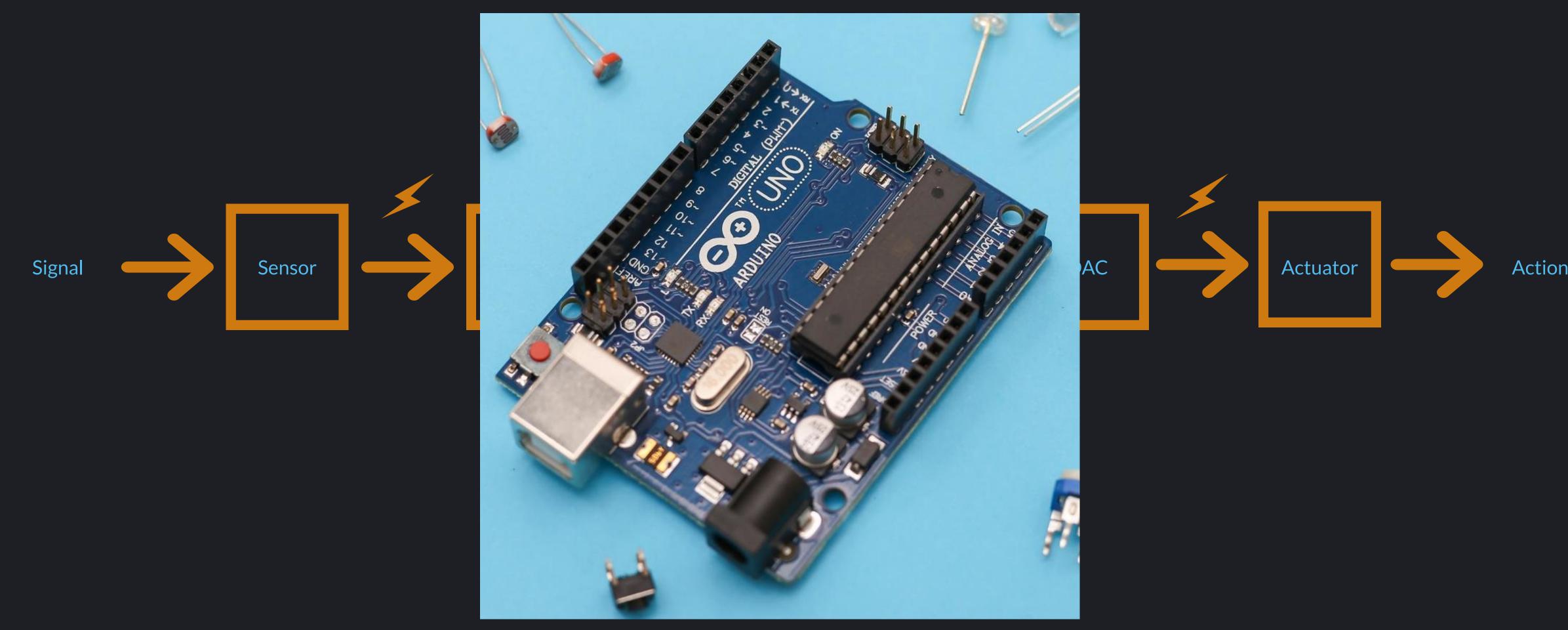

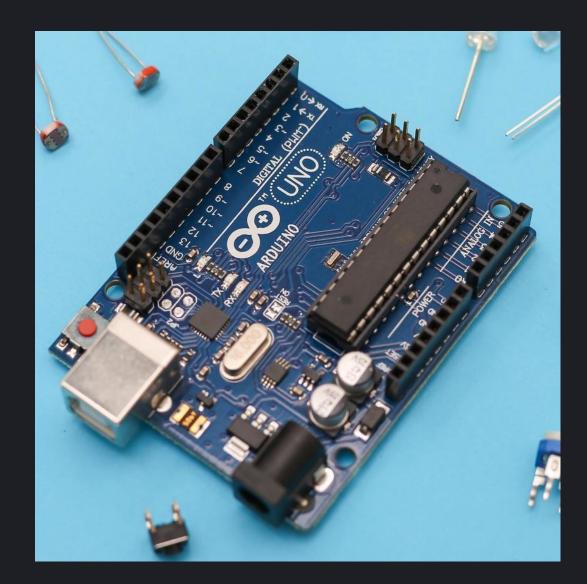

### Digital Programmable Electronics **AKA Microcontrollers**

and FPGA

# **Digital Programmable Electronics**

## Digital Programmable Electronics

### The advantages of Digital

- Fixed noise (only ADC and DAC)

- Infinite transformation complexity

- Fast and cheap design cycles, just recompile

- Reusable components with near infinite reuse

We still use 30 years old design today in new products

- Modules with well known input/output relationship

- Well known composition functions

101

Oh

- "just plumbing signals between these"

- Easy to debug, the "real" signal can always be probed

credit: Foone, https://twitter.com/Foone

- Well known composition functions

- "just plumbing signals between these"

- Easy to debug, the "real" signal can always be probed

Modules with well known input/output relationship

- Well known composition functions

- "just plumbing signals between these"

- Easy to debug, the "real" signal can always be probed

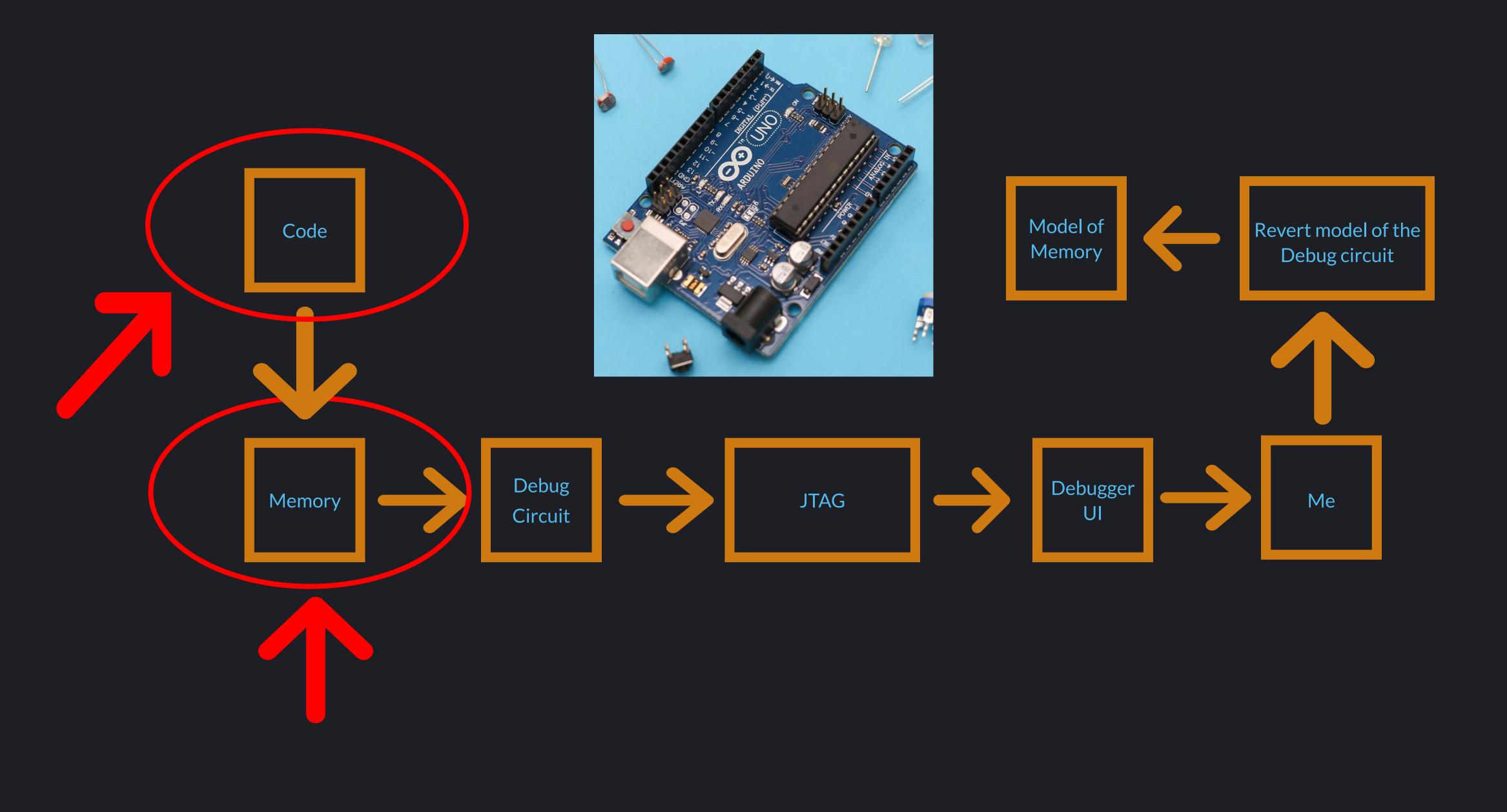

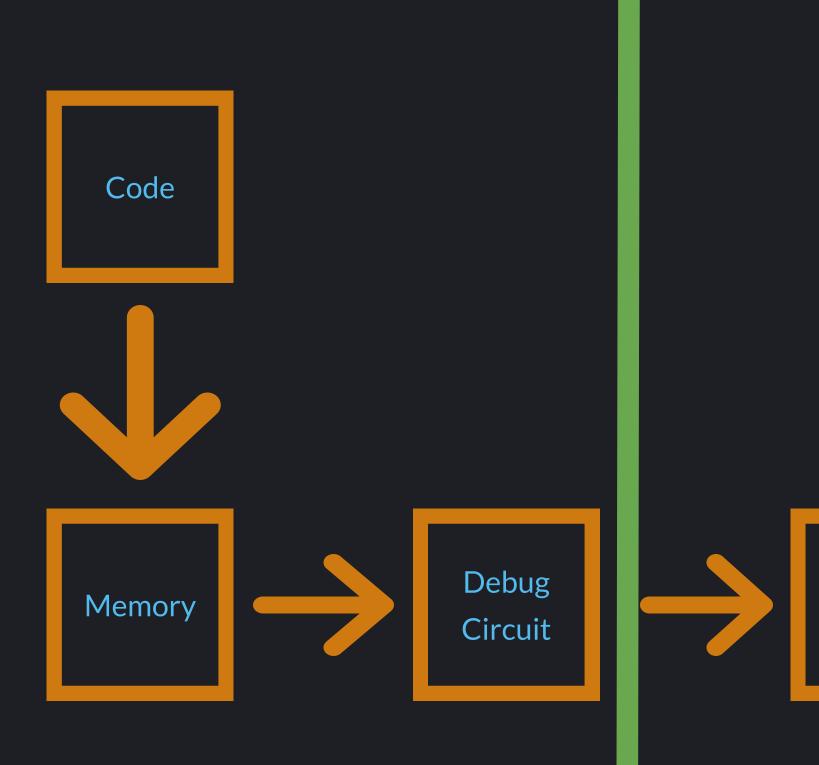

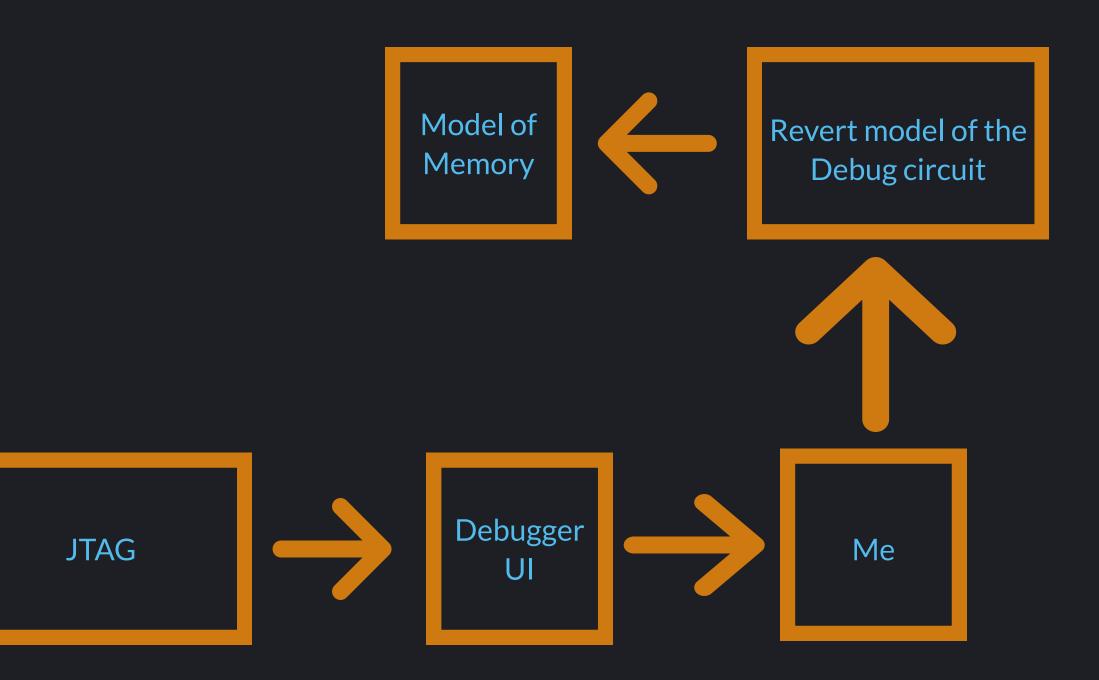

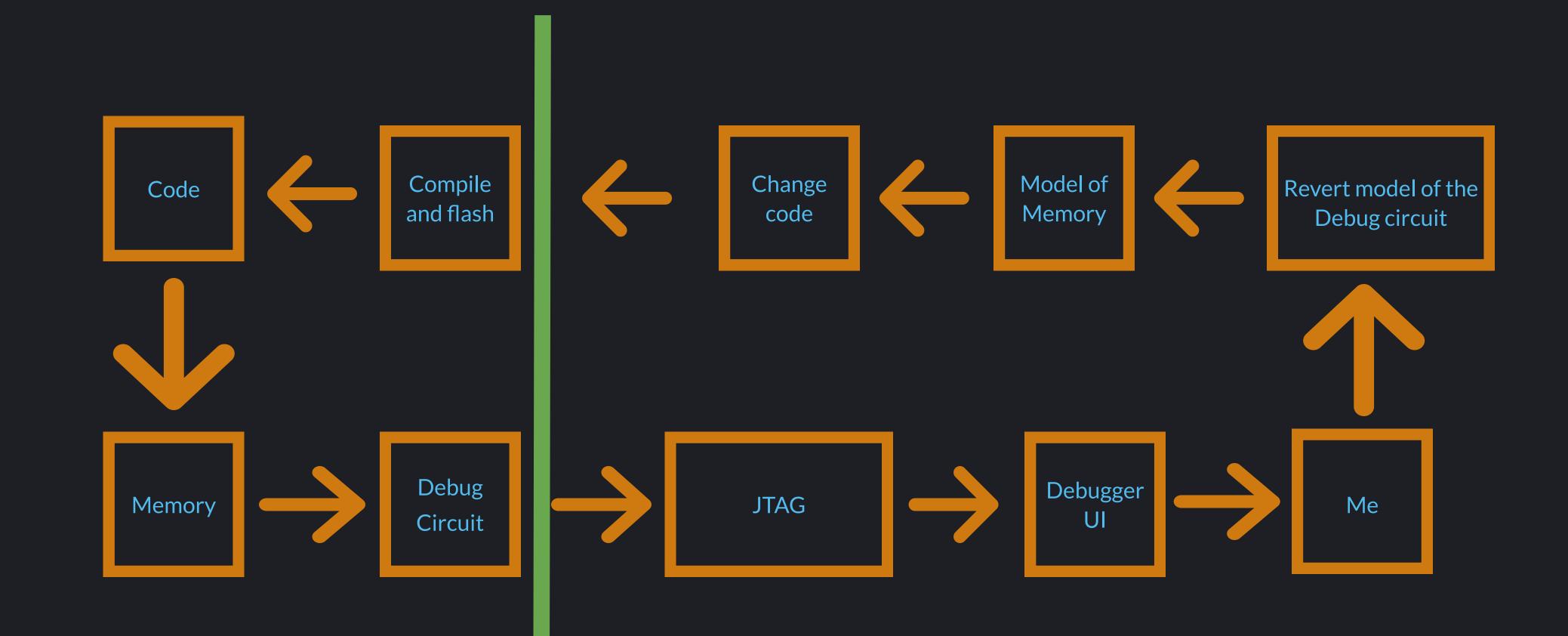

#### • Easy to debug, the "real" signal can always be probed

#### • Easy to debug, the "real" signal can always be probed

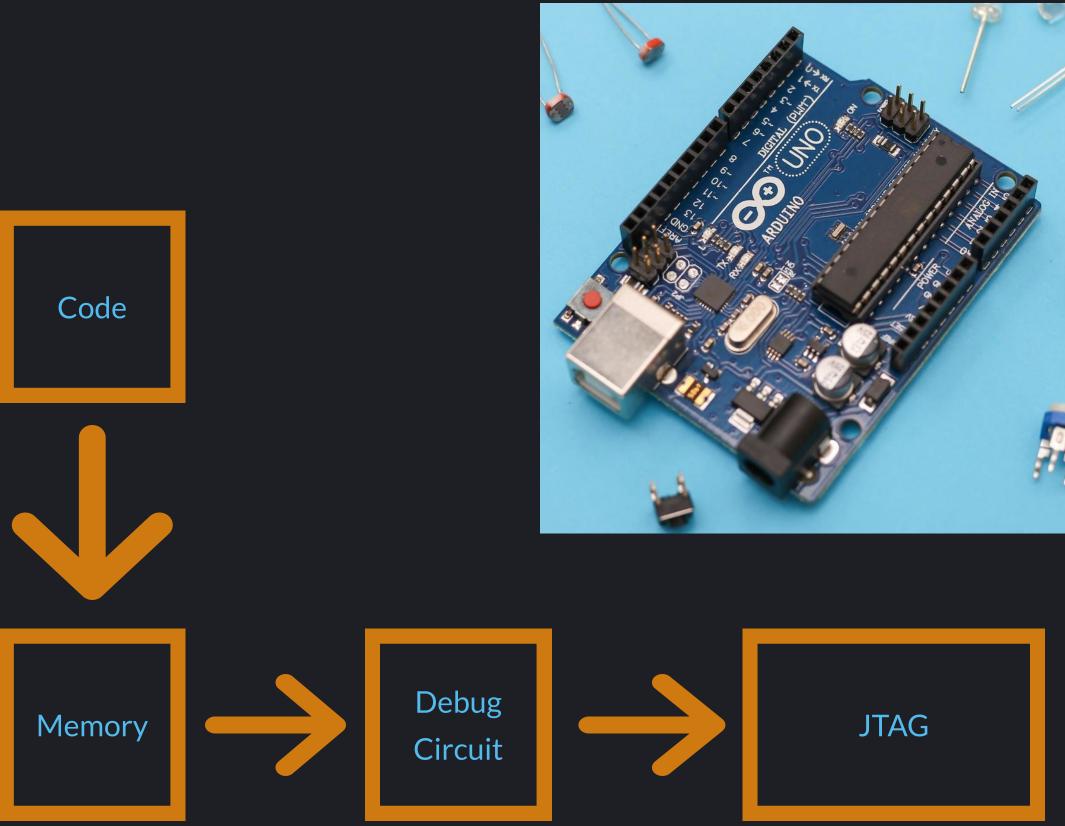

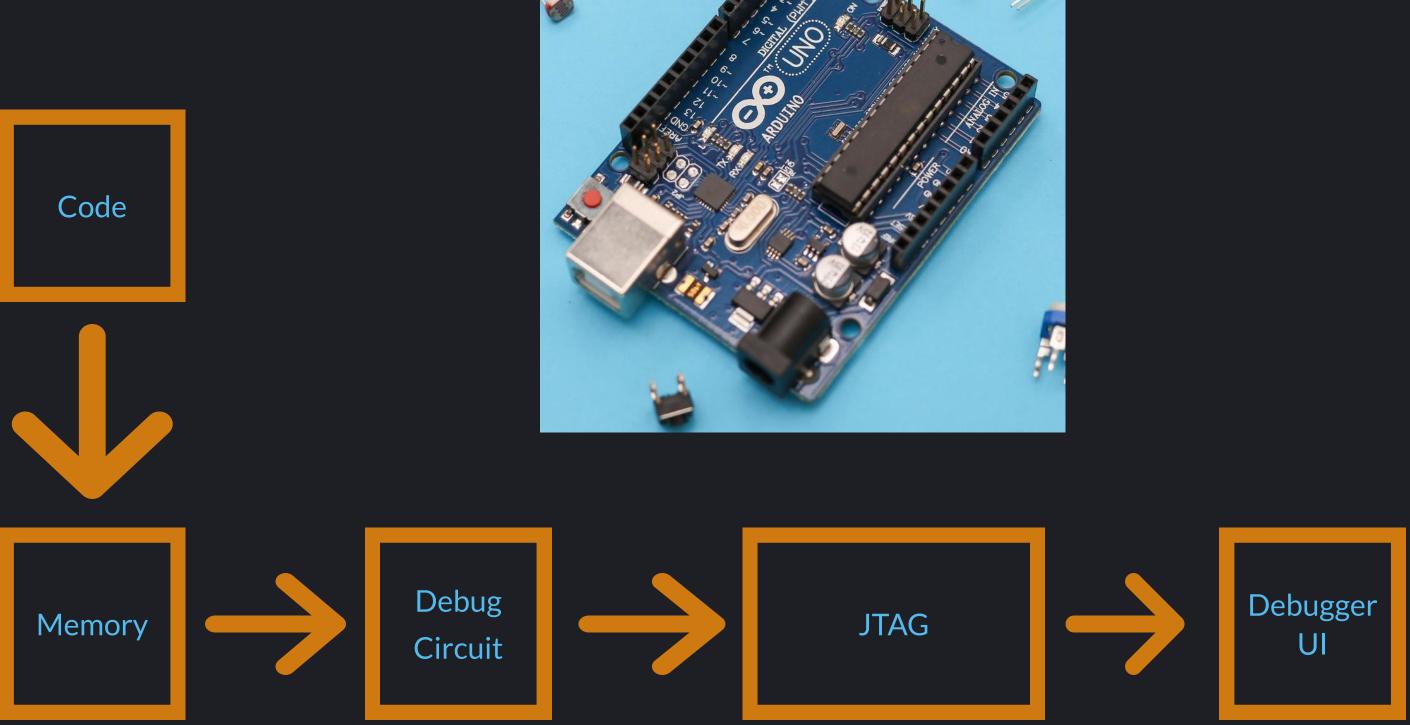

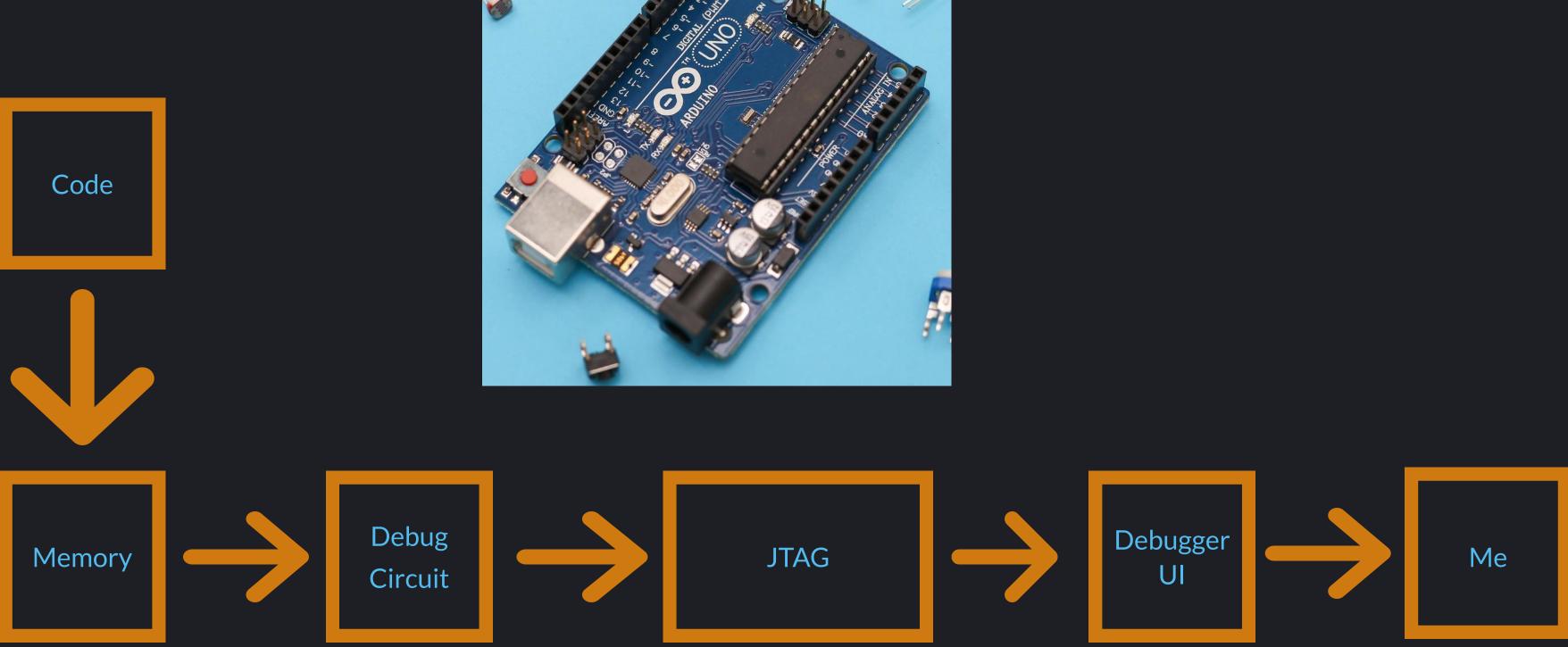

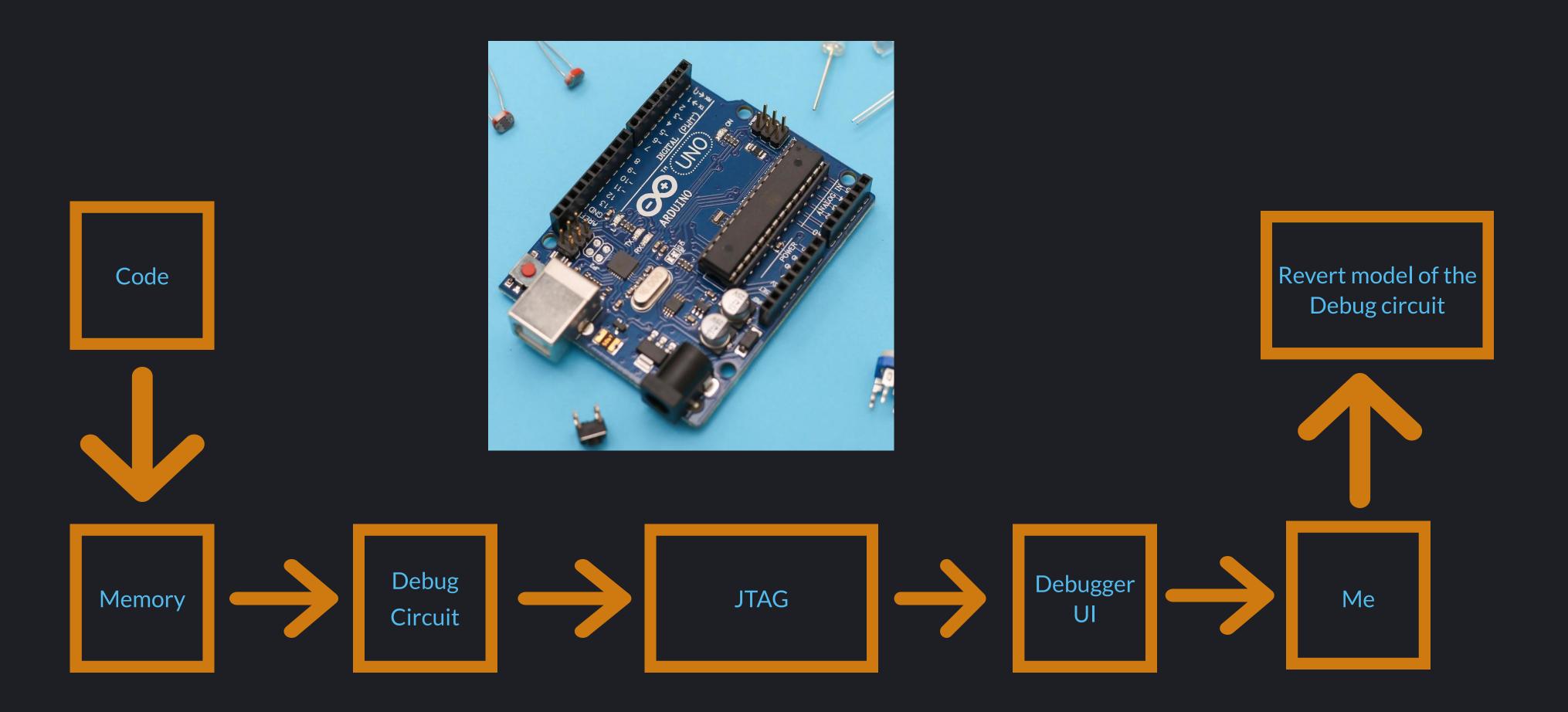

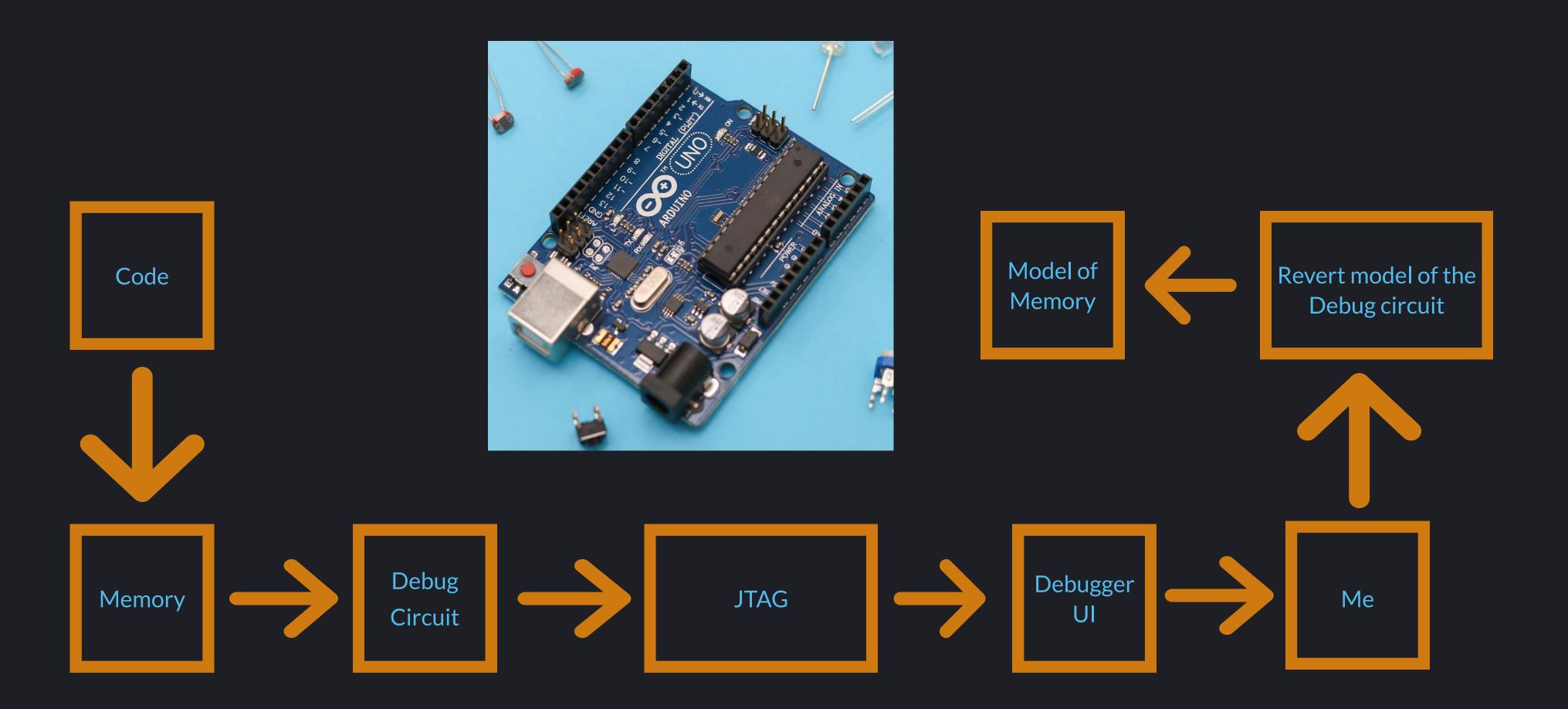

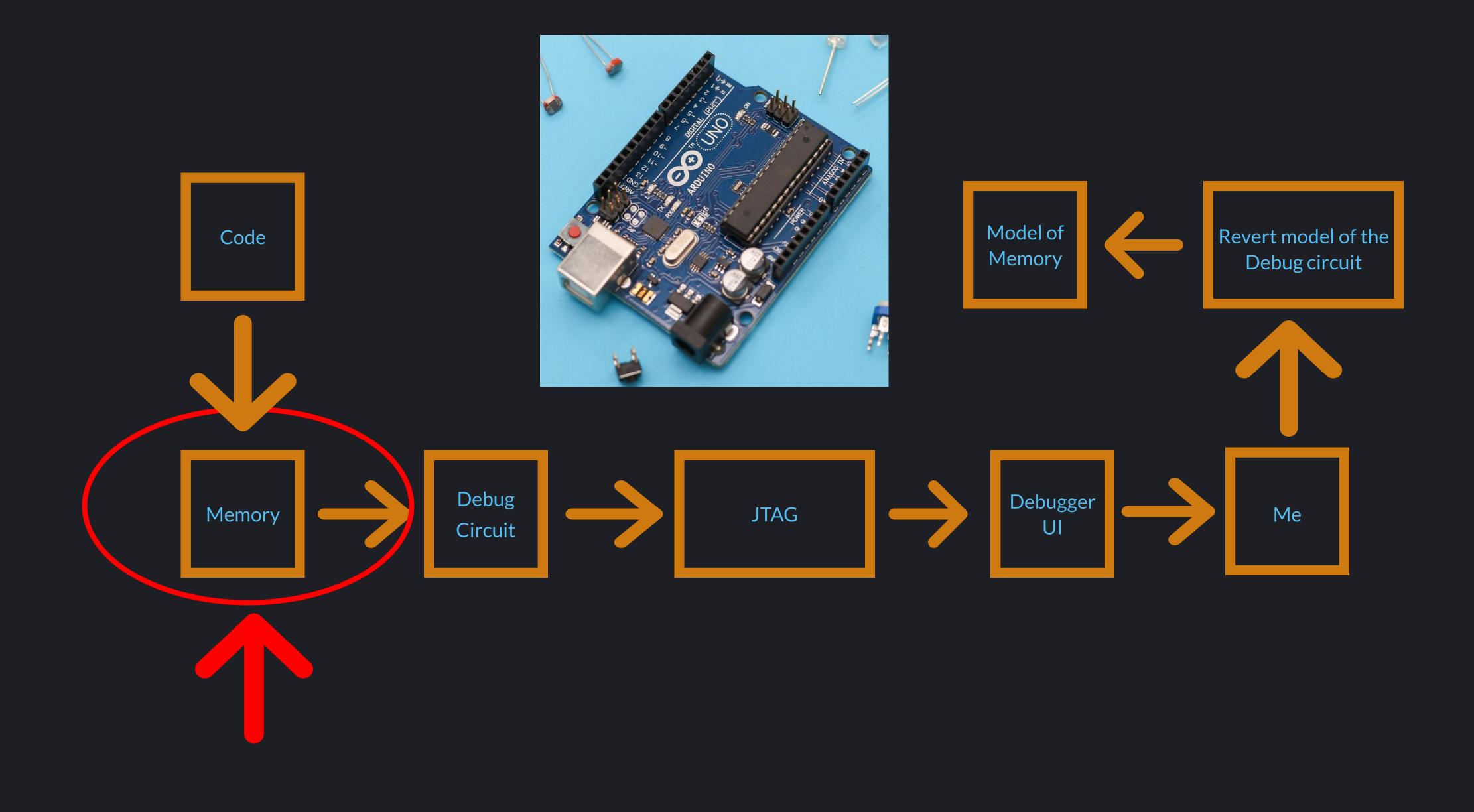

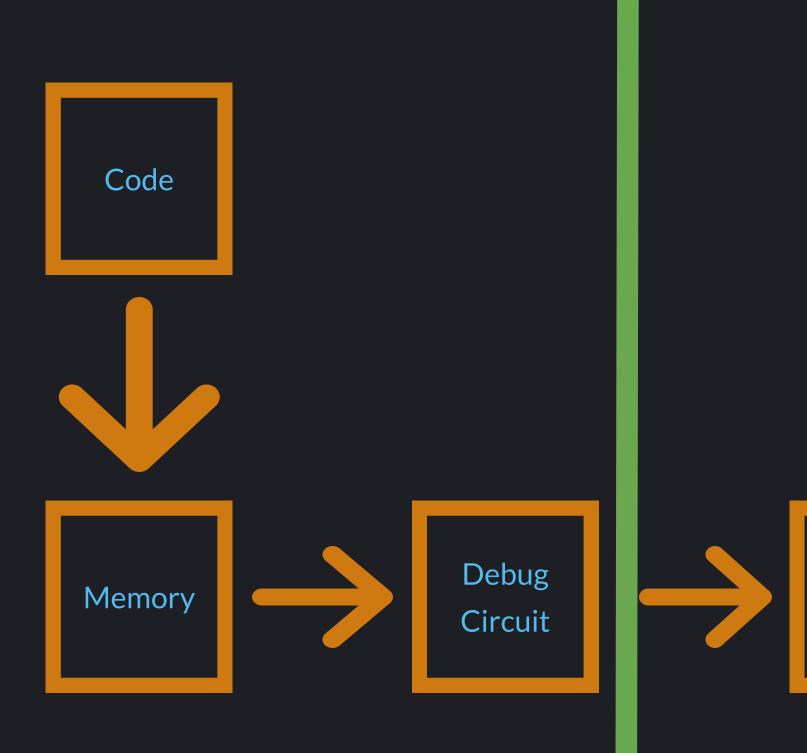

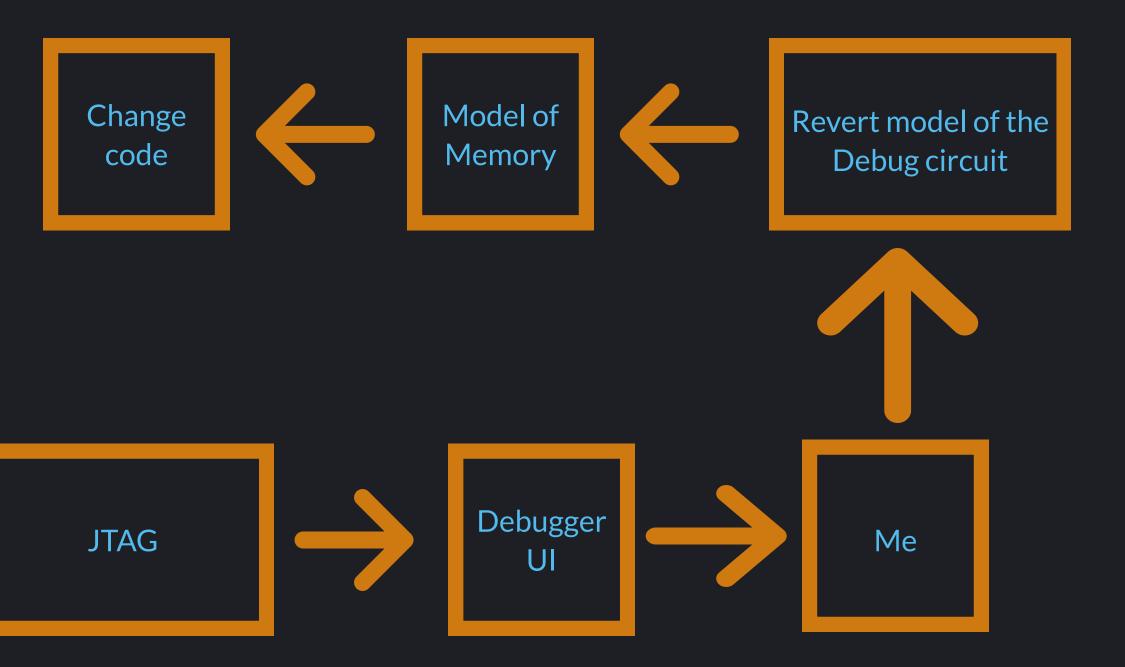

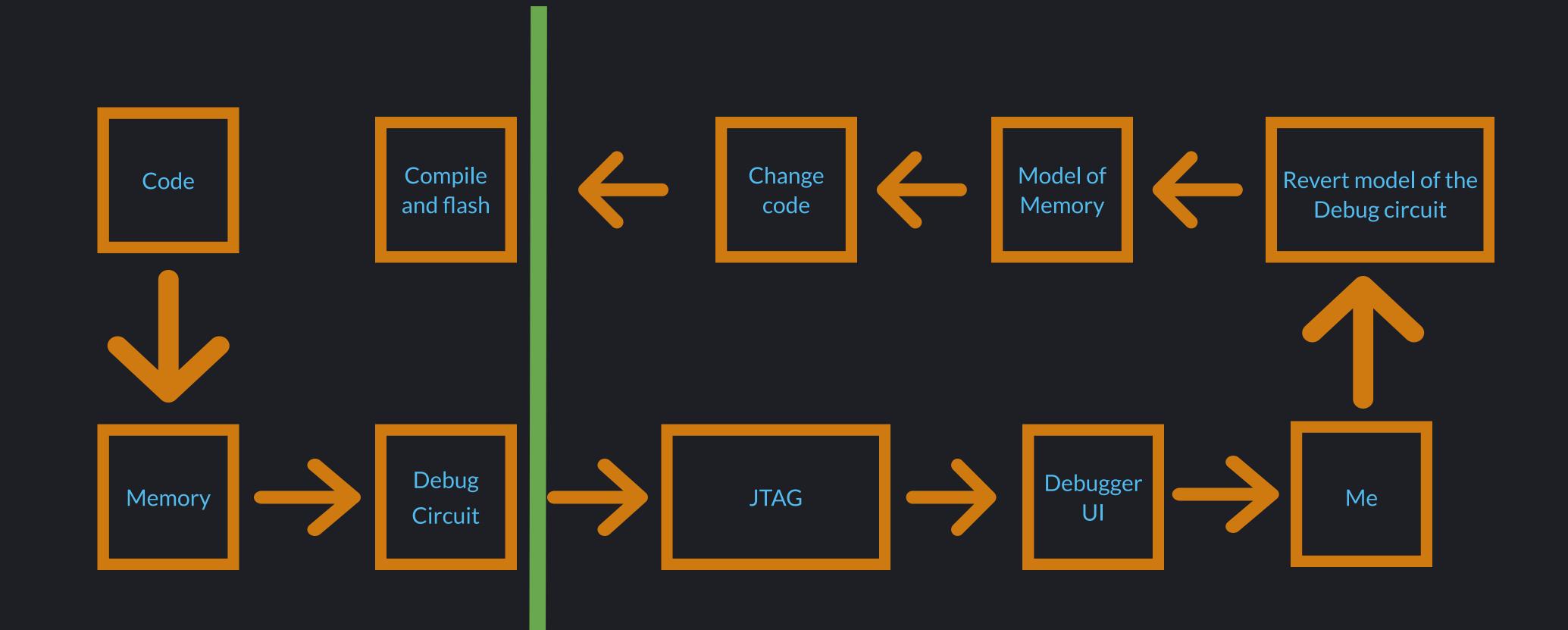

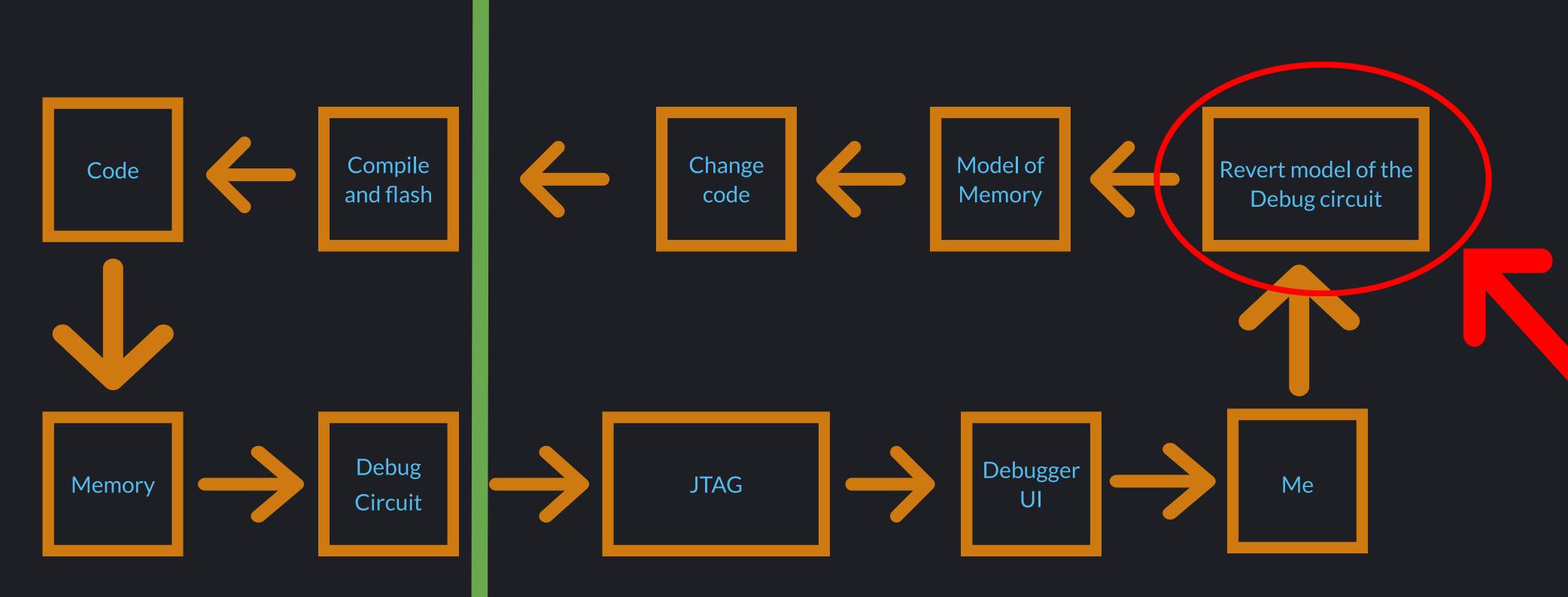

Memory Debug Circuit

Code

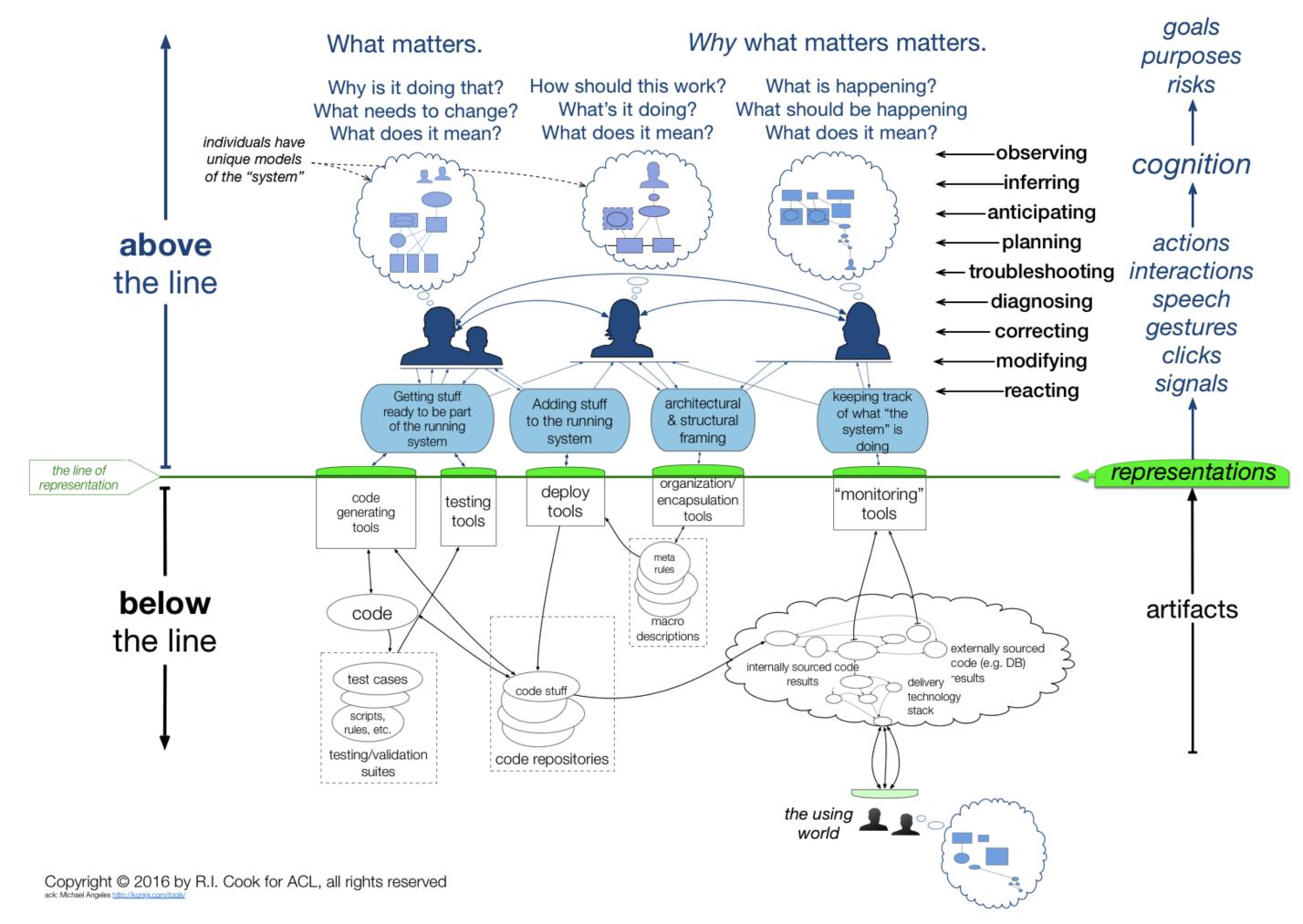

## Line of Representation

## Ceci N'Est Pas Un CPU Load

Thomas Depierre haruspex.dev @Di4naO